CS7620 Просмотр технического описания (PDF) - Cirrus Logic

Номер в каталоге

Компоненты Описание

Список матч

CS7620 Datasheet PDF : 70 Pages

| |||

CS7620

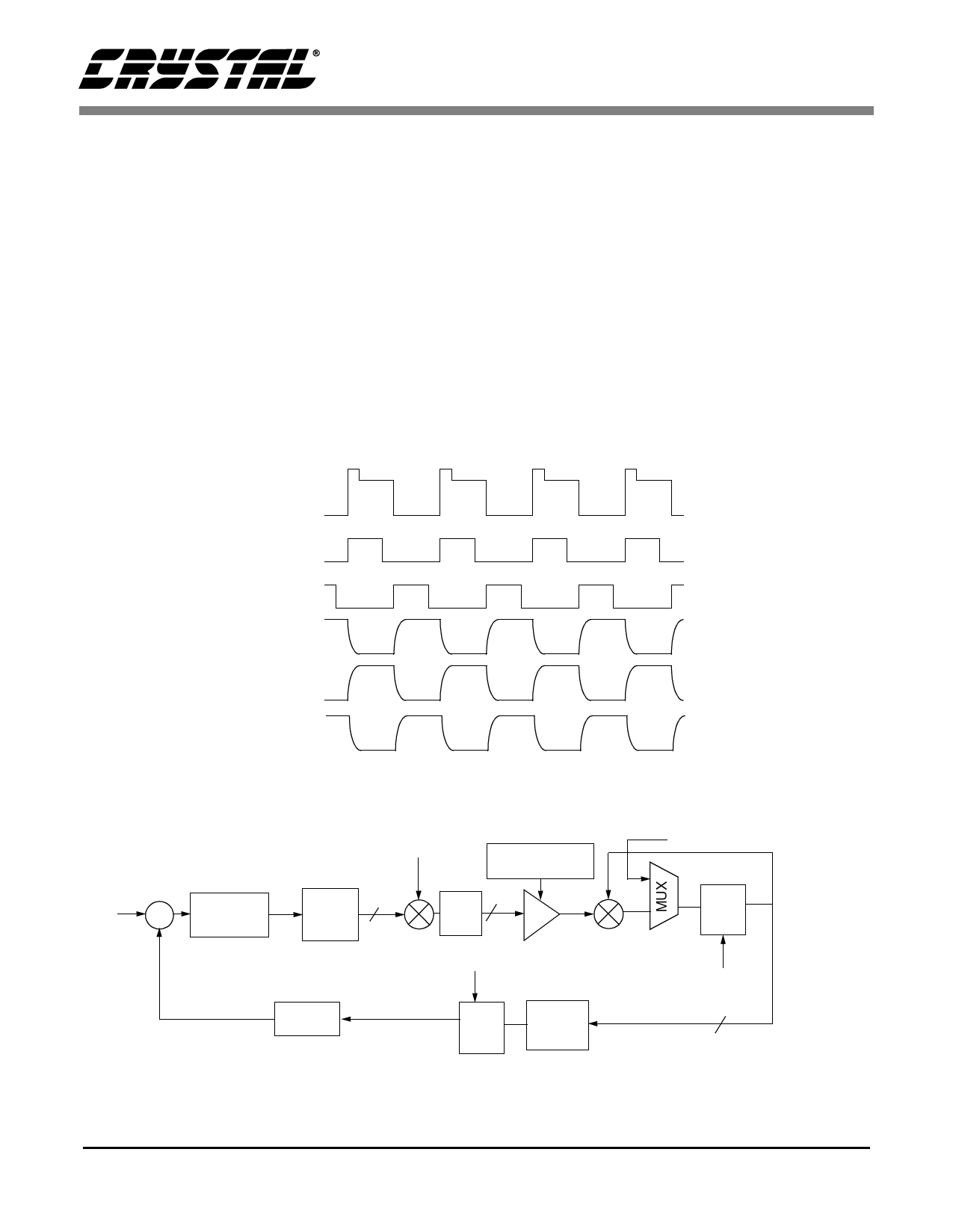

sets the black level value at the output of the ADC

to 64 in the 13 bit digital code. This loop is active

during the optically black pixels which are output

at the beginning and end of a frame as well as dur-

ing a portion of the horizontal blanking period. The

presence of black pixels in the CCD output is indi-

cated by the CLAMP pulse, which can either be

supplied externally or generated internally if the

timing for the CCD is generated by the CS7620.

The black level can also be written to through the

serial port.

In order to acquire a starting value for the black lev-

el, the loop will run over the several lines of black

pixels at the beginning of the frame. The block di-

agram of the loop is shown in Figure 10. The up-

date rate is once per line during active pixel lines,

and once every (n + 10) pixels during the optical

black lines.

CCD

INPUT

SIGNAL

Φ1

V(1)

V(2)

V(3)

Φ2

OUT OF

STAGE 1

OUT OF

STAGE 2

OUT OF

STAGE 3

V(1)

V(2)

V(3)

V(1)

V(2)

V(3)

V(1)

V(2)

Figure 9. Idealized timing diagram of VGA/CDS circuit

VIN

Σ

CDS/VGA

ADC

‘64’

BLK LVL LOOP

GAIN REG

10 +

7

+

- CLIP

K

+

FU

DAC

FU = UPDATE FREQUENCY

FP = PIXEL FREQUENCY

BINARY

Z-1

TO

THERM

Figure 10. Black level adjustment loop

FROM SERIAL INTERFACE

Z-1

FP

9

DS301PP2

11