ZR36050 Просмотр технического описания (PDF) - Unspecified

Номер в каталоге

Компоненты Описание

Список матч

ZR36050 Datasheet PDF : 52 Pages

| |||

ADVANCE INFORMATION

ZR36050

INTERFACES

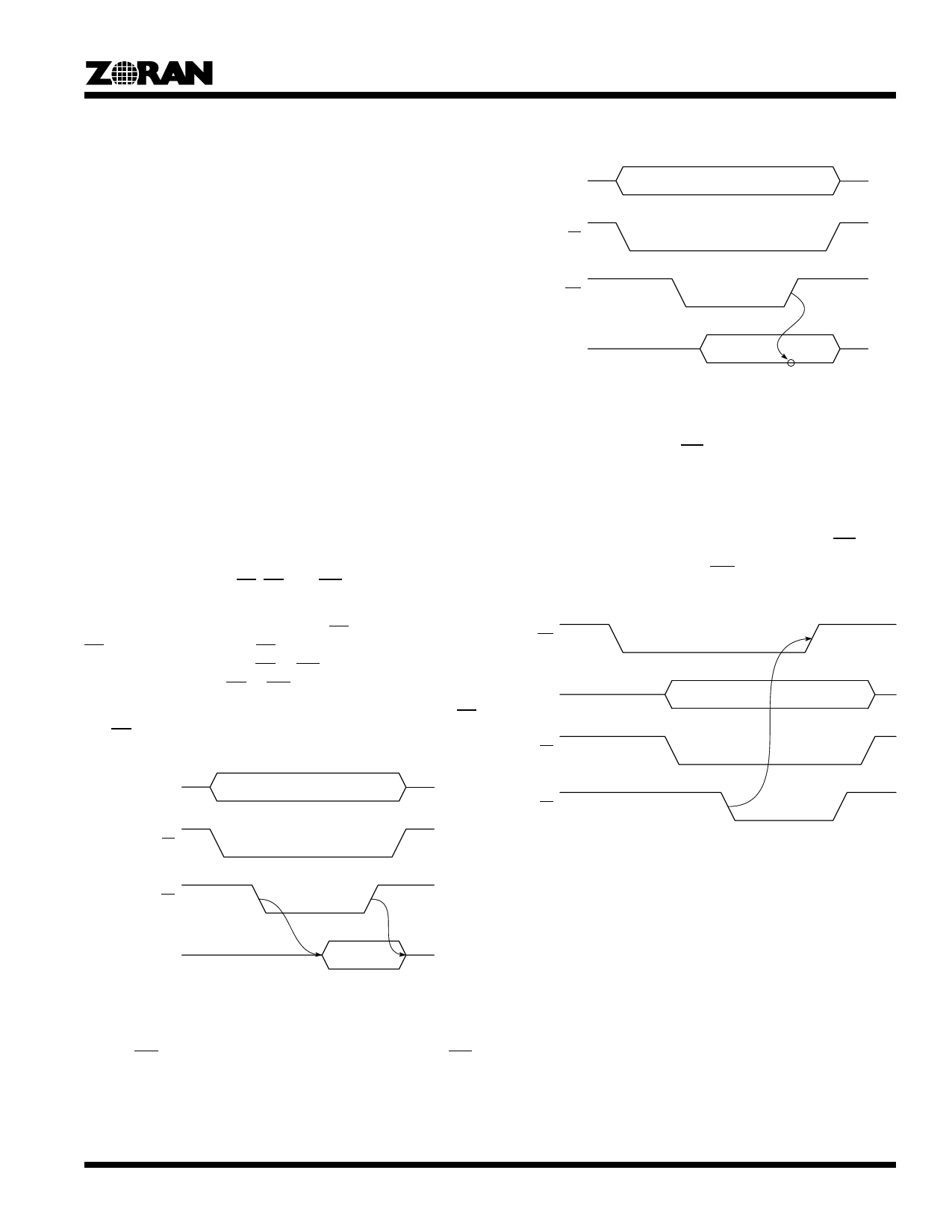

In the diagrams illustrating operation of the interfaces, an arrow

linking signal transitions indicates the causal relationship of the

transitions. An arrow terminating on a circle designates the point

ADDR

at which the indicated signal is sampled.

Host Interface

The Host Interface is used to access the Internal Memory

(Control Registers and JPEG Marker Segments) of the

ZR36050. It can also optionally be used to transfer the com-

pressed data to and from the ZR36050. There are 4 categories

of host interface bus cycle:

s Internal Memory read and write by the host

s Interrupt acknowledgment

s Slave mode Compressed Data Transfer

s DMA mode Compressed Data Transfer

Note that, although the Host Interface behaves as an asynchro-

nous interface, its control signals are internally synchronized to

CLK_IN, and CLK_IN must be toggling and enabled by CLKEN

in order for the Host Interface to operate.

Internal Memory Read and Write

Internal Memory read and write by the host is always 8 bits wide,

using the DATA, ADDR, CS, RD, and WR signal pins.

Figure 8 and Figure 9 show read and write cycles, respectively.

A bus cycle starts when the host drives CS low, and ends when

CS goes high. ADDR and CS must be stable throughout the

cycle and must overlap the RD or WR pulse. ADDR is sampled

with the falling edge of RD or WR.

In a read cycle, the Host Interface drives the DATA bus when CS

and RD are both active.

CS

WR

DATA (in)

SAMPLE

DATA

Figure 9. Parameter Write by Host

Interrupt Acknowledgment Cycle

The Host Interface activates INT when one of the STATUS_0 or

STATUS_1 register bits (with the exception of the DATRDY bit)

becomes active, and the corresponding bit in INT_REQ_0 or

INT_REQ_1 is set. When the host reads the status register con-

taining the active bit, or gives the GO command, the status

register is cleared and the Host Interface deactivates INT.

Figure 10 shows activation of INT, and its deactivation in

response to a status read.

INT

ADDR

ADDRESS OF STATUS REGISTER

CS

ADDR

RD

CS

RD

DATA (out)

Figure 8. Parameter Read by Host

In a write cycle the Host Interface latches the data on the rising

edge of WR. Data must be valid before the trailing edge of WR;

it need not be valid before the leading edge. Note that the GO

command is a write of arbitrary data to address 0.

Figure 10. Interrupt Acknowledgment by Read

of the Status Register

Slave Mode Compressed Data Transfer

In Slave mode, the host reads the compressed data from the

memory-mapped Compressed Data register in encoding, or

writes it into this register in decoding. Compressed data transfers

can be 8 or 16 bits wide, as specified by the BSWD bit in the

HARDWARE register. In a 16 bit transfer, the CODE bus acts as

an extension of the DATA bus. The lower numbered byte (the

byte that would have been transferred earlier in 8 bit transfers) is

read or written on the CODE or DATA bus, depending on the

BELE bit in the HARDWARE register. In 16-bit transfers, if the

last transfer of compressed data requires only one byte, the

ZR36050 appends a FF byte to complete the 16 bits in encoding,

and in decoding, the host can append an arbitrary byte.

19