CS5525-BS Просмотр технического описания (PDF) - Cirrus Logic

Номер в каталоге

Компоненты Описание

Список матч

CS5525-BS Datasheet PDF : 29 Pages

| |||

CS5525 CS5526

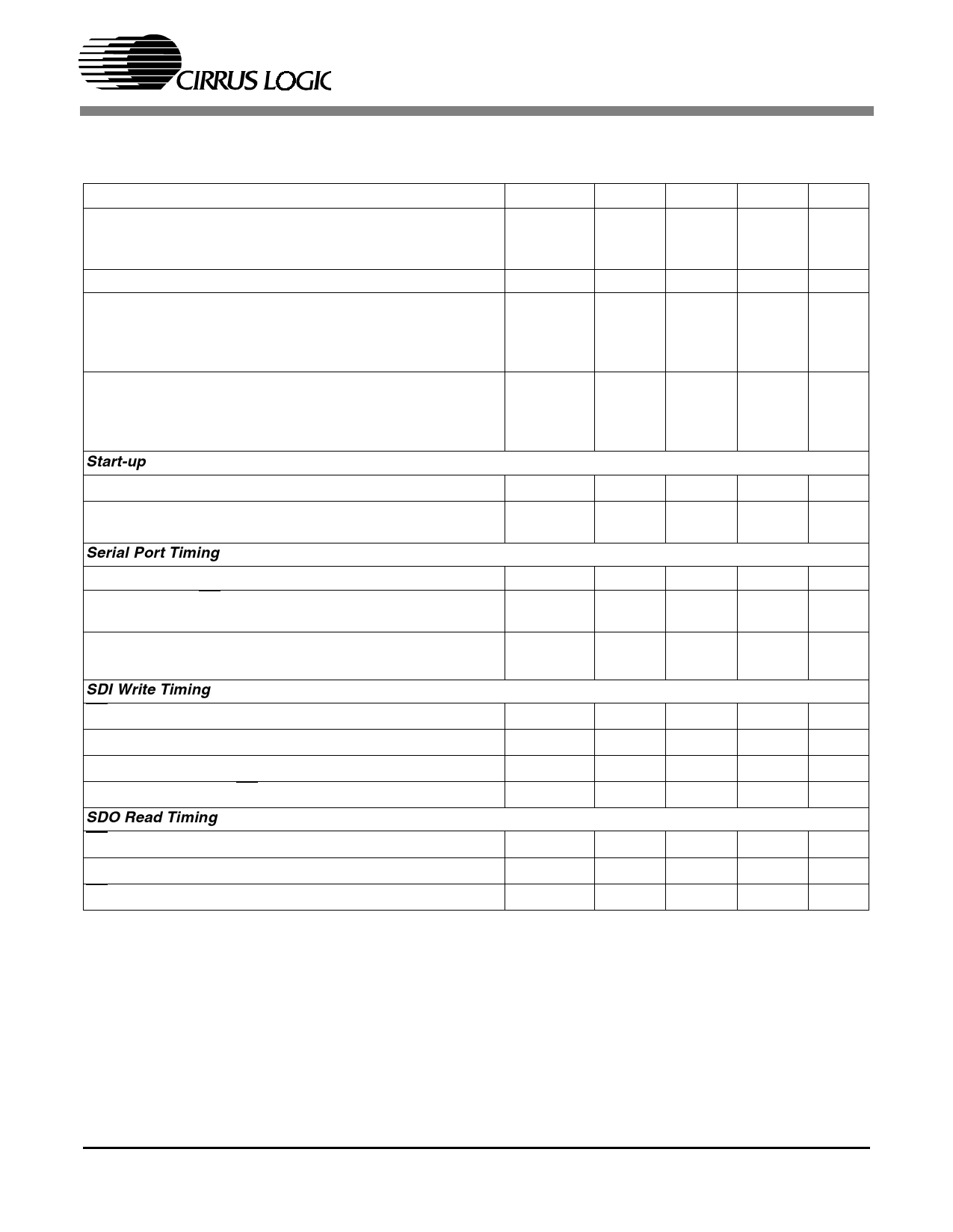

SWITCHING CHARACTERISTICS (TA = 25 °C; VA+ = 5 V ±5%; VD+ = 3.0 V ±10% or 5 V ±5%;

Input Levels: Logic 0 = 0 V, Logic 1 = VD+; CL = 50 pF.))

Parameter

Symbol Min

Typ

Max Unit

Master Clock Frequency

Master Clock Duty Cycle

(Note 19) XIN

Internal Clock

External Clock

30 32.768 36

kHz

30 32.768 100

40

-

60

%

Rise Times

(Note 20)

trise

Any Digital Input Except SCLK

SCLK

Any Digital Output

-

-

1.0

µs

-

-

100

µs

-

50

-

ns

Fall Times

(Note 20)

tfall

Any Digital Input Except SCLK

SCLK

Any Digital Output

-

-

1.0

µs

-

-

100

µs

-

50

-

ns

Start-up

Oscillator Start-up Time XTAL = 32.768 kHz (Note 21)

tost

Power-on Reset Period

tpor

-

500

-

ms

-

1003

-

XIN

cycles

Serial Port Timing

Serial Clock Frequency

SCLK

0

-

2

MHz

SCLK Falling to CS Falling for continuous running SCLK

t0

(Note 22)

Serial Clock

Pulse Width High

t1

Pulse Width Low

t2

SDI Write Timing

100

-

250

-

250

-

-

ns

-

ns

-

ns

CS Enable to Valid Latch Clock

Data Set-up Time prior to SCLK rising

Data Hold Time After SCLK Rising

SCLK Falling Prior to CS Disable

SDO Read Timing

t3

50

-

t4

50

-

t5

100

-

t6

100

-

-

ns

-

ns

-

ns

-

ns

CS to Data Valid

SCLK Falling to New Data Bit

CS Rising to SDO Hi-Z

t7

-

-

150

ns

t8

-

-

150

ns

t9

-

-

150

ns

Notes: 19. Device parameters are specified with a 32.768 kHz clock; however, clocks up to 100 kHz can be used

for increased throughput.

20. Specified using 10% and 90% points on waveform of interest. Output loaded with 50 pF.

21. Oscillator start-up time varies with crystal parameters. This specification does not apply when using an

external clock source.

22. Applicable when SCLK is continuously running.

6

DS202F3