CS5516-ASZ Просмотр технического описания (PDF) - Cirrus Logic

Номер в каталоге

Компоненты Описание

Список матч

CS5516-ASZ Datasheet PDF : 41 Pages

| |||

CS5516, CS5520

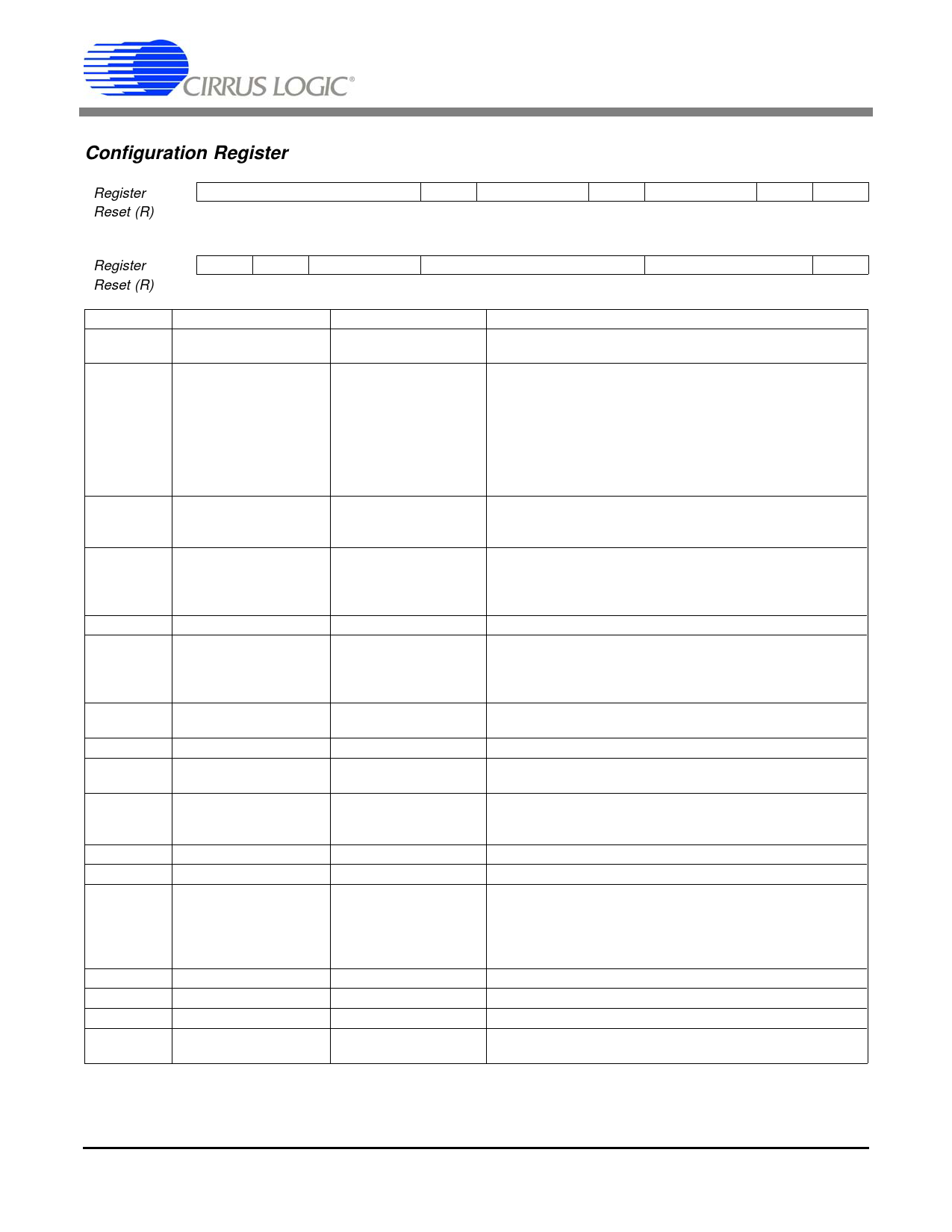

Configuration Register

D23 D22 D21 D20 D19 D18 D17 D16 D15 D14 D13 D12

Register

DAC3 DAC2 DAC1 DAC0 EXC F1

F0 D16 G1

G0 U/B D12

Reset (R)

0

0

0

0

0

0

0

0

0

0

0

0

Register

Reset (R)

D11 D10 D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

A/S EC

D9

D8 CC3 CC2 CC1 CC0 D3

D2

D1

RF

0

0

0

0

0

0

0

0

0

0

0

0

BIT

DAC3

DAC2-0

NAME

DAC Sign Bit

DAC Bits

EXC

F1-F0

Excitation: Internal

External

Select Frequency

D16

G1-G0

D16

Select PGA Gain

U/B

Select Unipolar/Bipo-

lar Mode

D12

D12

A/S

Awake/Sleep

EC

Execute Calibration

D9

D8

CC3-CC0

D9

D8

Calibration Control Bits

D3

D3

D2

D2

D1

D2

RF

Reset Filter

VALUE

0

R1

1

000

R

001

010

011

100

101

110

111

0

R

1

00

R

01

10

11

0

R

00

R

10

01

11

0

R

1

0

R

0

R

1

0

R

1

0

R

0

R

0000

R

1000

0100

0010

0001

0

R

0

R

0

R

0

R

1

Add Offset

Subtract Offset

FUNCTION

This bit is read only2

25% Offset

50% Offset

75% Offset

100% Offset

125% Offset

150% Offset

175% Offset

These bits are read only2

BX1 and BX2 outputs are determined by bits F1 and F0

BX1 is an input which determines the phase of the

demodulation clock and the BX2 output

Excitation on BX1 & BX2 is dc. BX1=0 V, BX2=+5 V

Excitation Frequency on BX1 & BX2 is XIN/8192 Hz

Excitation Frequency on BX1 & BX2 is XIN/16384 Hz

Excitation Frequency on BX1 & BX2 is XIN/4096 Hz

Must always be logic 0

Gain = 1 (X25)

Gain = 2 (X25)

Gain = 4 (X25)

Gain = 8 (X25)

Bipolar Measurement Mode

Unipolar Measurement Mode

Must always be logic 0

Awake Mode

Sleep Mode

Calibration not active

Perform calibration selected by CC3-CC0 bits. EC bit

must be written back to "0" after calibration is completed

Must always be logic 0

Must always be logic 0

No calibration to be performed

Calibrate non-ratiometric offset, VREF

Calibrate non-ratiometric offset, AIN

Calibrate ratiometric offset, AIN

Calibrate gain, AIN

Must always be logic 0

Must always be logic 0

Must always be logic 0

Normal operation

Reset Filter

Notes: 1.Reset State

2.A write to these bits does not change the register bit values. These bits are just a mirror of the DAC register contents.

Table 2. Configuration Register

DS74F21

13