CDB5126 Просмотр технического описания (PDF) - Cirrus Logic

Номер в каталоге

Компоненты Описание

Список матч

CDB5126 Datasheet PDF : 32 Pages

| |||

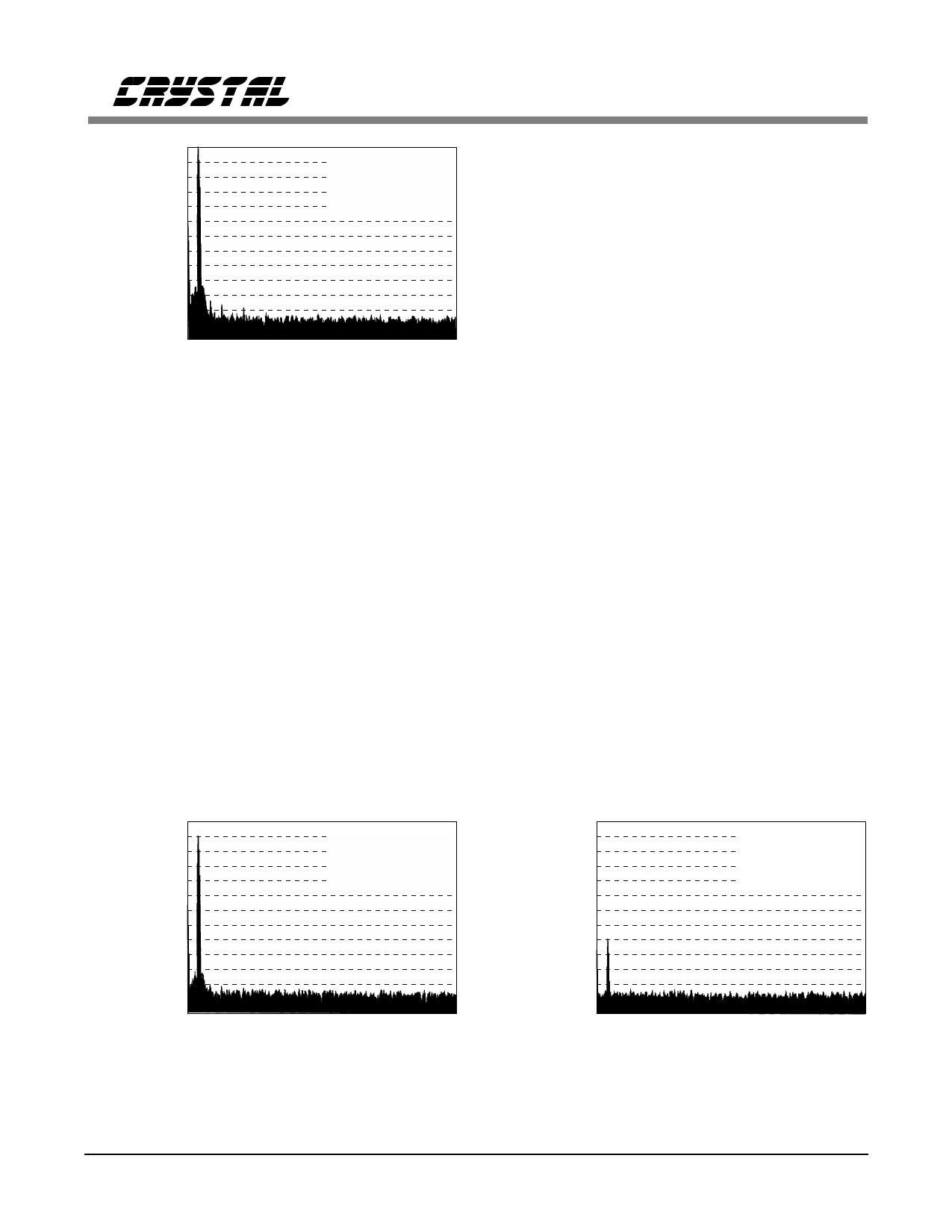

CS5126

0dB

-20dB

-40dB

-60dB

Signal

Amplitude

Relative to

Full Scale

-80dB

-100dB

-120dB

1 kHz

Sampling Rate: 48 kHz

Full Scale: 9V p-p

S/(N+D): 91.75 dB

S/(N+D): 92.53 dB

(dc to 20 kHz)

Input Frequency

24kHz

Figure 4. FFT Plot of CS5126 in Stereo Mode

(Left Channel with 1 kHz, Full-Scale Input)

Differential Nonlinearity

The self-calibration scheme utilized in the

CS5126 features a calibration resolution of 1/4

LSB, or 18-bits. This ideally yields DNL of

±1/4 LSB, with code widths ranging from 3/4 to

5/4 LSB’s. This insures consistent sound quality

independent of signal level.

Traditional laser trimmed ADC’s have signifi-

cant differential nonlinearities which are disas-

trous to sound quality with low-level signals.

Appearing as wide and narrow codes, DNL

often causes entire sections of the transfer func-

tion to be missing. Although their affect is minor

on S/(N+D) with high amplitude signals, DNL

errors dominate performance with low-level sig-

nals. For instance, a signal 80dB below full-

scale will slew past only 6 or 7 codes. Half of

those codes could be missing with a conven-

tional hybrid ADC capable of only 14-bit DNL.

The most common source of DNL errors in con-

ventional ADC’s is bit weight errors. These can

arise due to accuracy limitations in factory trim

stations, thermal or physical stresses after cali-

bration, and/or drifts due to aging or temperature

variations in the field. Bit-weight errors have a

drastic effect on a converter’s ac performance.

They can be analyzed as step functions superim-

posed on the input signal. Since bits (and their

errors) switch in and out throughout the transfer

curve, their effect is signal dependent. That is,

harmonic and intermodulation distortion, as well

as noise, can vary with different input condi-

tions.

Differential nonlinearities in successive-approxi-

mation ADC’s also arise due to dynamic errors

in the comparator. Such errors can dominate if

the converter’s throughput/sampling rate is

driven too high. The comparator will not be al-

lowed sufficient time to settle during each bit

decision in the successive-approximation algo-

0dB

-20dB

-40dB

Sampling Rate: 48 kHz

Full Scale: 9V p-p

S/(N+D): 83.27 dB

S/(N+D): 84.06 dB

(dc to 20 kHz)

Signal

Amplitude

Relative to

Full Scale

-60dB

-80dB

-100dB

-120dB

1 kHz

Input Frequency

a. Left Channel with 1 kHz, -10 dB Input

24kHz

0dB

-20dB

-40dB

Sampling Rate: 48 kHz

Full Scale: 9V p-p

S/(N+D): 13.70 dB

S/(N+D): 14.49 dB

(dc to 20 kHz)

Signal

Amplitude

Relative to

Full Scale

-60dB

-80dB

-100dB

-120dB

1 kHz

Input Frequency

b. Left Channel with 1 kHz, -80 dB Input

24kHz

Figure 5. FFT Plots of CS5126 in Stereo Mode

8

DS32F1