OZ6812 Просмотр технического описания (PDF) - O2Micro International

Номер в каталоге

Компоненты Описание

Список матч

OZ6812 Datasheet PDF : 13 Pages

| |||

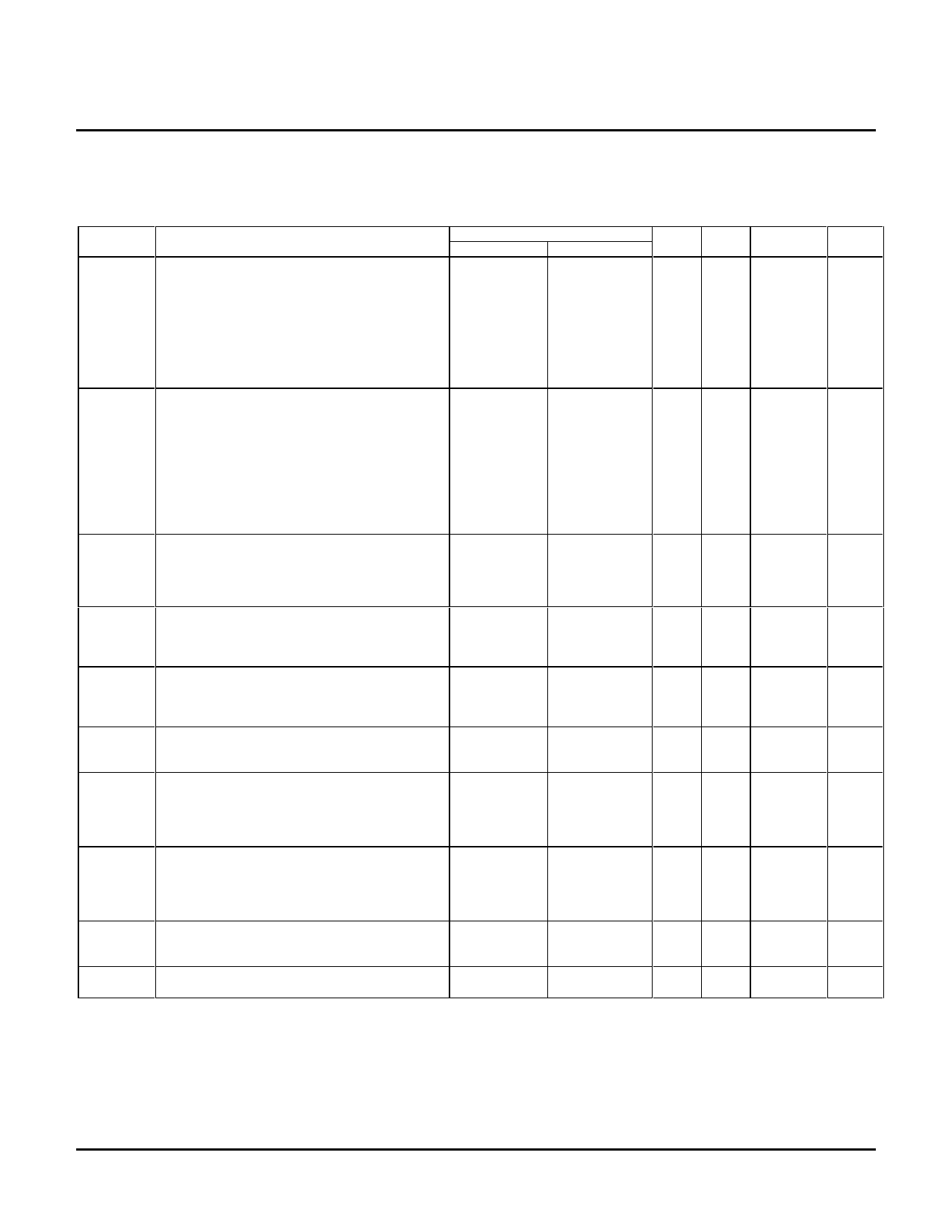

Pin List

Bold Text = Normal Default Pin Name

OZ6812

PCI Bus Interface Pins

Pin Name

AD[31:0]

C/BE[3:0]#

FRAME#

IRDY#

TRDY#

STOP#

IDSEL

DEVSEL#

PERR#

SERR#

Description

PCI Bus Address Input / Data: These pins

connect to PCI bus signals AD[31:0]. A Bus

transaction consists of an address phase followed

by one or more data phases.

PCI Bus Command / Byte Enable: The

command signaling and byte enables are

multiplexed on the same pins. During the address

phase of a transaction, C/BE[3:0]# are interpreted

as the bus commands. During the data phase,

C/BE[3:0]# are interpreted as byte enables. The

byte enables are to be valid for the entirety of

each data phase, and they indicate which bytes in

the 32-bit data path are to carry meaningful data

for the current data phase.

Cycle Frame: This input indicates to the OZ6812

that a bus transaction is beginning. While

FRAME# is asserted, data transfers continue.

When FRAME# is de-asserted, the transaction is

in its final phase.

Initiator Ready: This input indicates the initiating

agent’s ability to complete the current data phase

of the transaction. IRDY# is used in conjunction

with TRDY#.

Target Ready: This output indicates target

Agent's the OZ6812’s ability to complete the

current data phase of the transaction. TRDY# is

used in conjunction with IRDY#.

Stop: This output indicates the current target is

requesting the master to stop the current

transaction.

Initialization Device Select: This input is used as

a chip select during configuration read and write

transactions. This is a point-to-point signal.

IDSEL can be used as a chip select during

configuration read and write transactions.

Device Select: This output is driven active LOW

when the PCI address is recognized as

supported, thereby acting as the target for the

current PCI cycle. The Target must respond

before timeout occurs or the cycle will terminate.

Parity Error: The output is driven active LOW

when a data parity error is detected during a write

phase.

System Error: This output is driven active LOW

to indicate an address parity error.

Pin Number

LQFP

BGA

3-5, 7-11, 15- D4, B1, C2-1,

17, 19, 23-26, D2, E4, D1, E3,

38-41, 43, 45- F3, F1, F2, G1,

47, 49, 51-57 H2-3, J1, H4,

M2, K4, N2,

M3, N3, K5,

N4, L5, N5, L6,

N6, M6, L7, N7,

M7, K7

12, 27, 37, 48 E2, J2, N1, M5

28

K1

29

J3

31

L1

33

K3

13

E1

32

J4

34

M1

35

L2

Input

TTL

TTL

TTL

TTL

TTL

TTL

TTL

TTL

-

-

Type

I/O

I/O

I/O

I/O

I/O

I/O

I

I/O

TO

TO

Power

Rail

PCI_Vcc

PCI_Vcc

PCI_Vcc

PCI_Vcc

PCI_Vcc

PCI_Vcc

PCI_Vcc

PCI_Vcc

PCI_Vcc

PCI_Vcc

Drive

PCI

Spec

PCI

Spec

PCI

Spec

PCI

Spec

PCI

Spec

PCI

Spec

PCI

Spec

PCI

Spec

PCI

Spec

PCI

Spec

OZ6812-SF-1.5

Page 4