ICS671M-01 Просмотр технического описания (PDF) - Integrated Circuit Systems

Номер в каталоге

Компоненты Описание

Список матч

ICS671M-01 Datasheet PDF : 4 Pages

| |||

ICS671-01

Zero Delay, Low Skew Buffer and Multipler

Description

The ICS671-01 is a low phase noise, high speed

PLL based, 8 output, low skew zero delay buffer

and multiplier. Based on ICS’s proprietary low

jitter Phase Locked Loop (PLL) techniques, the

device provides eight low skew outputs at speeds

up to 160 MHz at 3.3 V. The ICS671-01 includes

a bank of six outputs running at either x2 or x4

mode, one output running at either x2, x4, or x5

mode, and one more output running at either x1,

x2, or x4 mode. For normal operation, output

clock CLK8 is tied to the FBIN pin.

ICS manufactures the largest variety of clock

generators and buffers, and is the largest clock

supplier in the world.

Features

• Packaged in 16 pin narrow SOIC

• Clock outputs from 5 to 160 MHz

• Zero input-output delay

• Integrated x2 or x4 selections, and x5 for CLK7

• Eight low-skew (<250 ps) outputs

• Full CMOS outputs with 25 mA output drive

capability at TTL levels

• Tri-state mode for board-level testing

• Advanced, low power, sub-micron CMOS process

• 3.3 V to 5 V operating voltage

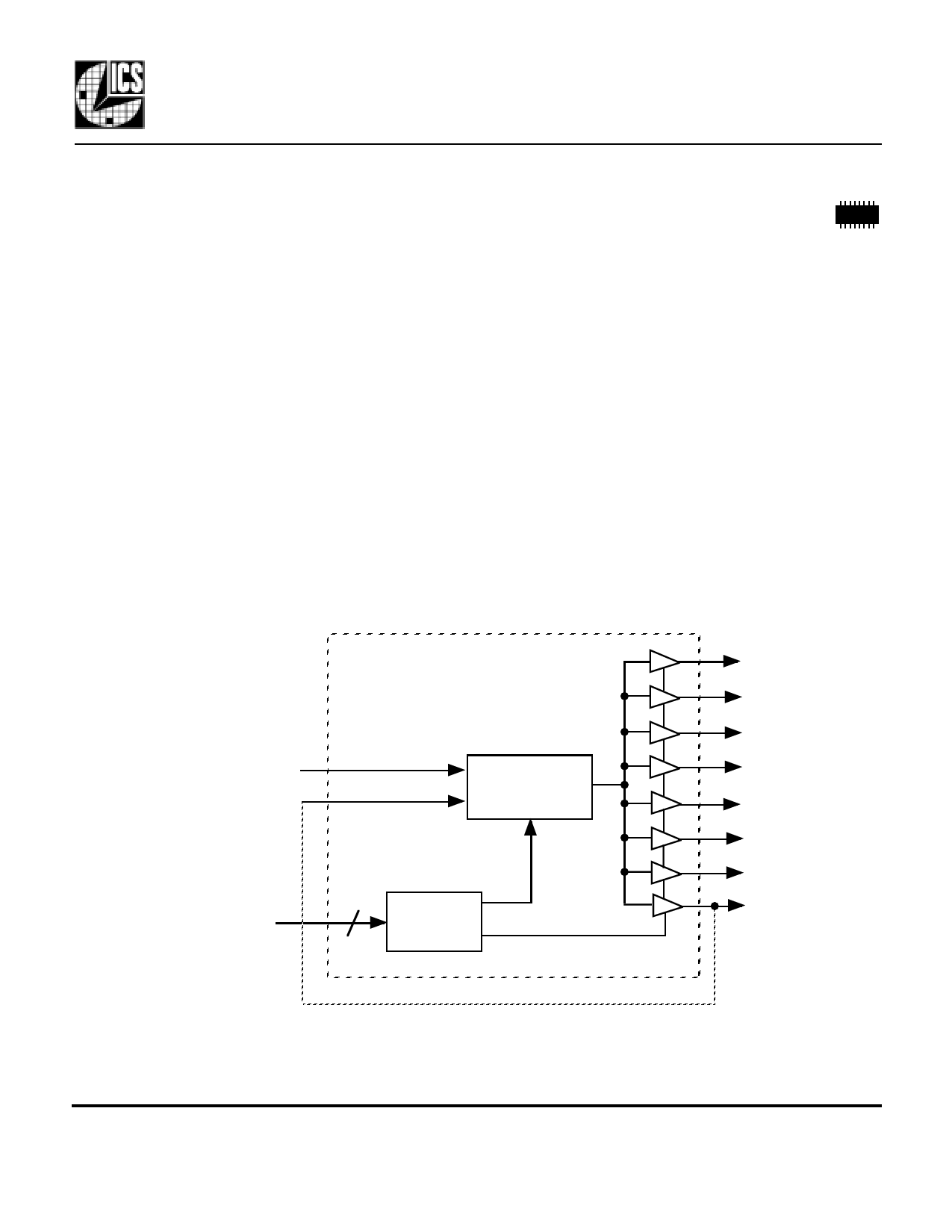

Block Diagram

CLKIN

FBIN

x2, x4, or x5

PLL

S1, S0

2

Control

Logic

CLK1

CLK2

CLK3

CLK4

CLK5

CLK6

CLK7

CLK8

MDS 671-01 B

1

Revision 051700

Printed 11/15/00

Integrated Circuit Systems, Inc.• 525 Race Street • San Jose •CA•95126• (408) 295-9800 tel • www.icst.com