UT1553B/BCRT-ACA0 Просмотр технического описания (PDF) - Aeroflex UTMC

Номер в каталоге

Компоненты Описание

Список матч

UT1553B/BCRT-ACA0

UT1553B/BCRT-ACA0 Datasheet PDF : 61 Pages

| |||

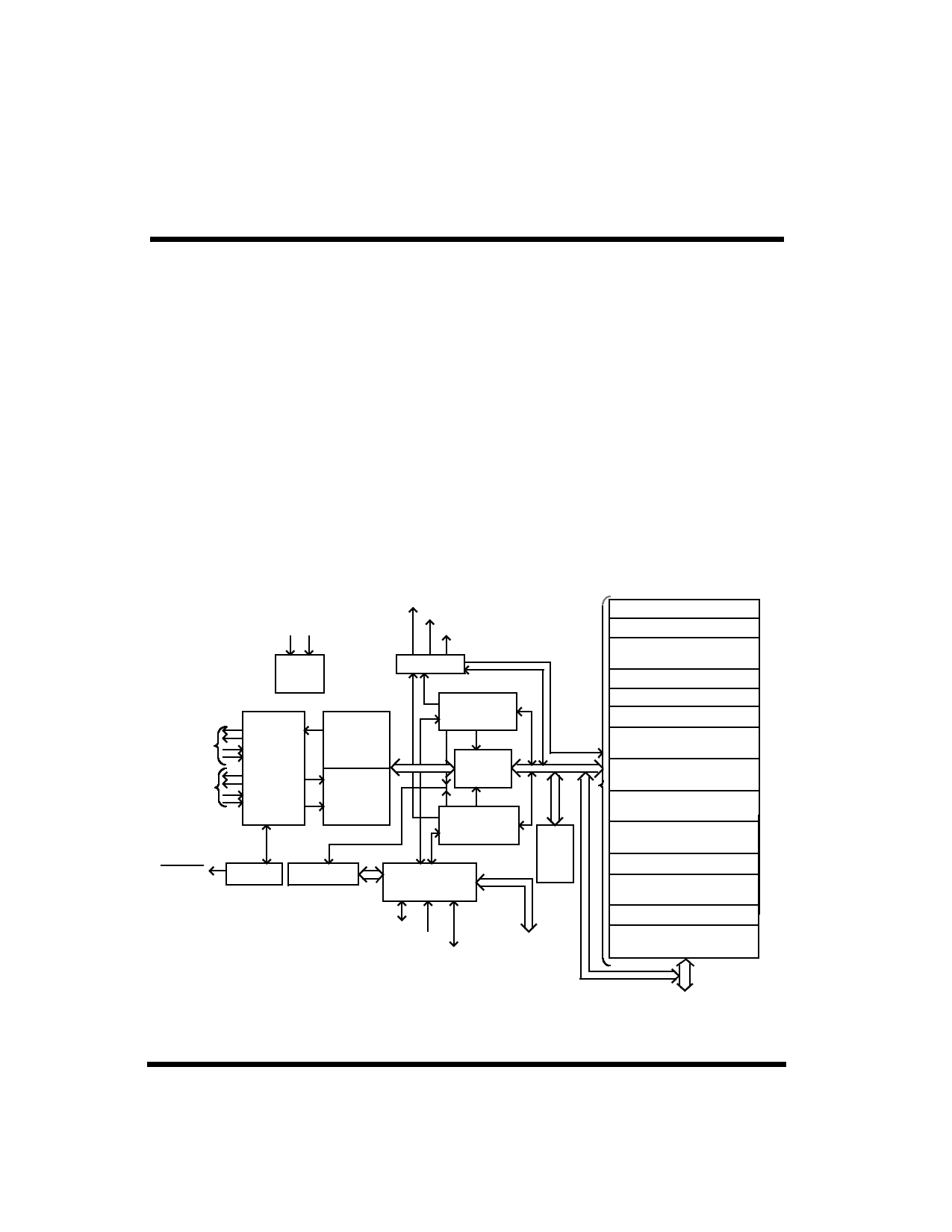

UT1553B BCRT

FEATURES

p Comprehensive MIL-STD-1553B dual-redundant

Bus Controller (BC) and Remote Terminal

(RT) functions

p MIL-STD-1773 compatible

p Multiple message processing capability in BC and

RT modes

p Time-tagging and message logging in RT mode

p Automatic polling and intermessage delay in

BC mode

p Programmable interrupt scheme and internally

generated interrupt history list

p Register-oriented architecture to enhance

programmability

p DMA memory interface with 64K addressability

p Internal self-test

p RemoteterminaloperationsinASD/ENASD-certified

(SEAFAC)

p The UT1553B BCRT is not available radiation-harden

ed

p Packaged in 84-pin pingrid array, 84- and 132-lead

flatpack, 84-lead leadless chip carrier packages

p Standard Microcircuit Drawing 5962-88628 available

- QML Q and V compliant

1553

DATA

CHANNEL

A

1553

DATA

CHANNEL

B

TIMERON

12MHZ

MASTER

RESET

HIGH-PRIORITY

STD PRIORITY LEVEL

STD PRIORITY PULSE

REGISTERS

CONTROL

STATUS

CLOCK &

RESET

LOGIC

DUAL

CHANNEL

ENCODER/

DECODER

MODULE

SERIAL to

PARALLEL-

CONVER-

SION

PARALLEL-

TO-SERIAL

CONVER-

SION

INTERRUPT

HANDLER

BC PROTOCOL

& MESSAGE

HANDLER

16

BUS

TRANSFER

LOGIC

RT PROTOCOL

& MESSAGE

HANDLER

TIMEOUT

ADDRESS 16

GENERATOR

DMA/CPU

CONTROL

16

CURRENT BC BLOCK/

RT DESCRIPTOR SPACE

POLLING COMPARE

BUILT-IN-TEST WORD

CURRENT COMMAND

INTERRUPT LOG

LIST POINTER

16

HIGH-PRIORITY

INTERRUPT ENABLE

16

HIGH-PRIORITY

INTERRUPT STATUS/RESET

16

BUILT-

IN-

TEST

STANDARD INTERRUPT

ENABLE

RT ADDRESS

BUILT-IN-TEST

START COMMAND

DMA ARBITRATION

REGISTER CONTROL

DUAL-PORT MEMORY CONTROL

ADDRESS

PROGRAMMED RESET

RT TIMER TAG

RESET COMMAND

16

16

Figure 1. BCRT Block Diagram

DATA

BCRT-1