AD9432 Просмотр технического описания (PDF) - Analog Devices

Номер в каталоге

Компоненты Описание

Список матч

AD9432 Datasheet PDF : 20 Pages

| |||

AD9432

Spurious-Free Dynamic Range (SFDR)

The ratio of the rms signal amplitude to the rms value of the

peak spurious spectral component. The peak spurious compo-

nent may or may not be a harmonic. May be reported in dBc

(i.e., degrades as signal level is lowered), or in dBFS (always

related back to converter full scale).

Two-Tone Intermodulation Distortion Rejection

The ratio of the rms value of either input tone to the rms value

of the worst third order intermodulation product; reported in dBc.

Two-Tone SFDR

The ratio of the rms value of either input tone to the rms value

of the peak spurious component. The peak spurious component

may or may not be an IMD product. May be reported in dBc

(i.e., degrades as signal level is lowered), or in dBFS (always

related back to converter full scale).

Worst Harmonic

The ratio of the rms signal amplitude to the rms value of the

worst harmonic component, reported in dBc.

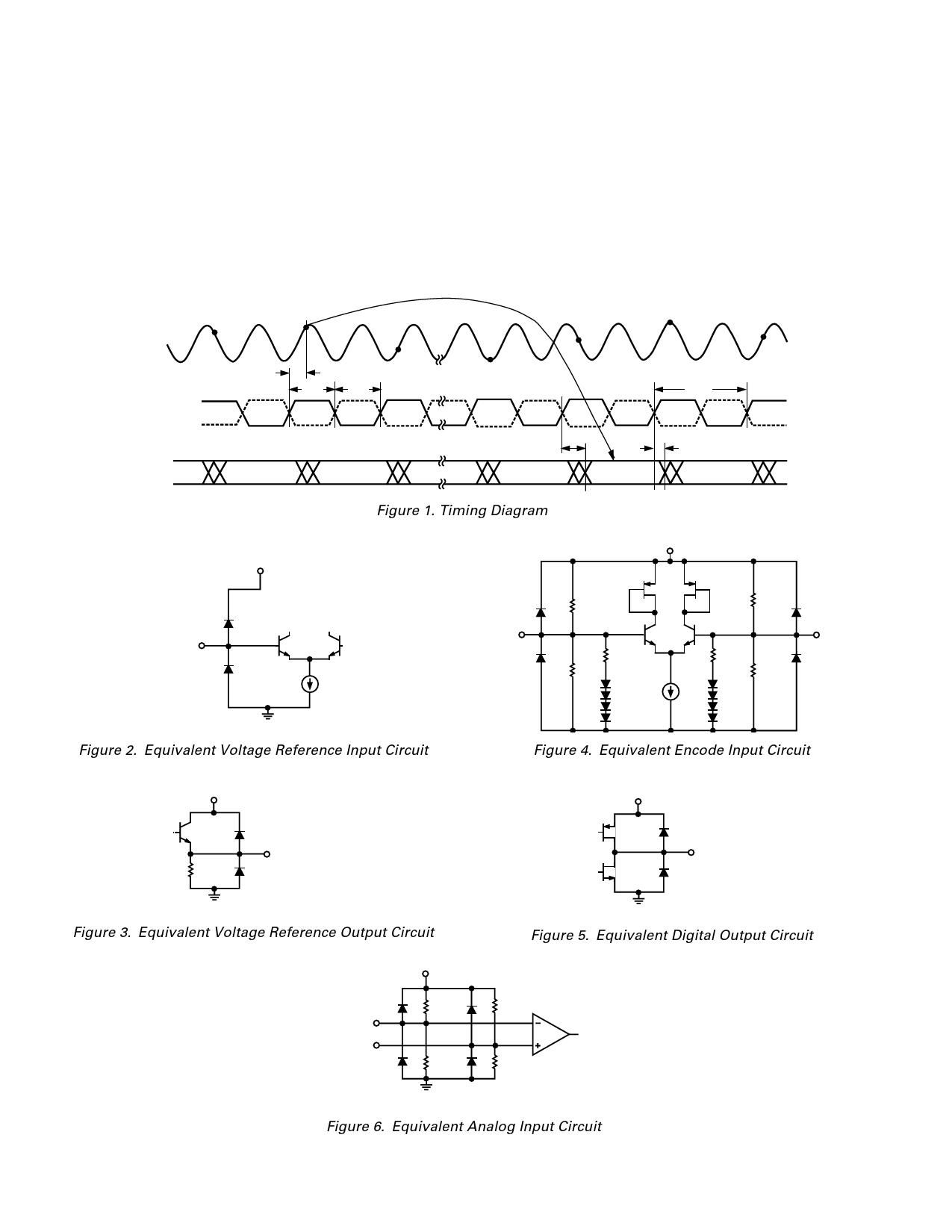

SAMPLE N–1

SAMPLE N

SAMPLE N+10

SAMPLE N+11

AIN

ENCODE

ENCODE

D11– D0

tA

t EH

SAMPLE N+1

t EL

SAMPLE N+9

DATA N–11

DATA N–10

N–9 N–2

t PD

DATA N–1

DATA N

1/fS

tV

DATA N + 1

Figure 1. Timing Diagram

VCC

VCC

VREFIN

ENCODE

17k⍀

100⍀

8k⍀

17k⍀

ENCODE

100⍀

8k⍀

Figure 2. Equivalent Voltage Reference Input Circuit

VCC

Q1

NPN

VREFOUT

Figure 4. Equivalent Encode Input Circuit

VDD

DIGITAL

OUTPUT

VREF OUTPUT

Figure 3. Equivalent Voltage Reference Output Circuit

VCC

DIGITAL OUTPUT

Figure 5. Equivalent Digital Output Circuit

5k⍀

5k⍀

AIN

AIN

7k⍀

7k⍀

ANALOG INPUT

Figure 6. Equivalent Analog Input Circuit

–6–

REV. E