QL5030 Даташит - QuickLogic Corporation

Architecture Overview

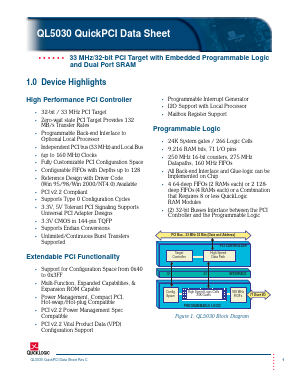

The QL5030 device in the QuickLogic QuickPCI ESP (Embedded Standard Product) family provides a complete and customizable PCI interface solution combined with 24,000 system gates of programmable logic. This device eliminates any need for the designer to worry about PCI bus compliance, yet allows for the maximum 32-bit PCI bus bandwidth (132 MB/s).

Device Highlights

High Performance PCI Controller

• 32-bit / 33 MHz PCI Target

• Zero-wait state PCI Target Provides 132 MB/s Transfer Rates

• Programmable Back-end Interface to Optional Local Processor

• Independent PCI bus (33 MHz) and Local Bus

• (up to 160 MHz) Clocks

• Fully Customizable PCI Configuration Space

• Configurable FIFOs with Depths up to 128

• Reference Design with Driver Code (Win 95/98/Win 2000/NT4.0) Available

• PCI v2.2 Compliant

• Supports Type 0 Configuration Cycles

• 3.3V, 5V Tolerant PCI Signaling Supports Universal PCI Adapter Designs

• 3.3V CMOS in 144-pin TQFP

• Supports Endian Conversions

• Unlimited/Continuous Burst Transfers Supported

Extendable PCI Functionality

• Support for Configuration Space from 0x40 to 0x3FF

• Multi-Function, Expanded Capabilities, & Expansion ROM Capable

• Power Management, Compact PCI, Hot-swap/Hot-plug Compatible

• PCI v2.2 Power Management Spec Compatible

• PCI v2.2 Vital Product Data (VPD) Configuration Support

• Programmable Interrupt Generator

• I2O Support with Local Processor

• Mailbox Register Support

Programmable Logic

• 24K System gates / 266 Logic Cells

• 9,216 RAM bits, 71 I/O pins

• 250 MHz 16-bit counters, 275 MHz Datapaths, 160 MHz FIFOs

• All Back-end Interface and Glue-logic can be Implemented on Chip

• 4 64-deep FIFOs (2 RAMs each) or 2 128- deep FIFOs (4 RAMs each) or a Combination that Requires 8 or less QuickLogic RAM Modules

• (2) 32-bit Busses Interface between the PCI Controller and the Programmable Logic