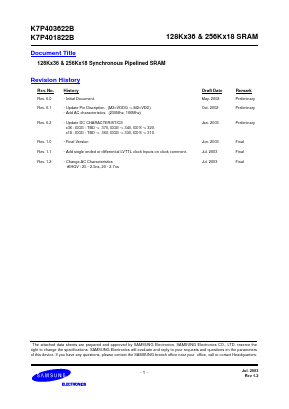

K7P401822B Даташит - Samsung

FUNCTION DESCRIPTION

The K7P403622B and K7P401822B are 4,718,592 bit Synchronous Pipeline Mode SRAM devices. They are organized as 131,072 words by 36 bits for K7P403622B and 262,144 words by 18 bits for K7P401822B, fabricated using Samsungs advanced CMOS technology.

FEATURES

• 128Kx36 or 256Kx18 Organizations.

• 3.3V VDD, 2.5/3.3V VDDQ.

• LVTTL Input and Output Levels.

• Differential, PECL clock / Single ended or differential LVTTL clock Inputs

• Synchronous Read and Write Operation.

• Registered Input and Registered Output.

• Internal Pipeline Latches to Support Late Write.

• Byte Write Capability(four byte write selects, one for each 9bits)

• Synchronous or Asynchronous Output Enable.

• Power Down Mode via ZZ Signal.

• JTAG Boundary Scan (subset of IEEE std. 1149.1).

• 119(7x17)Pin Ball Grid Array Package(14mmx22mm).