IDT72V3622L10PFG Просмотр технического описания (PDF) - Integrated Device Technology

Номер в каталоге

Компоненты Описание

Список матч

IDT72V3622L10PFG

IDT72V3622L10PFG Datasheet PDF : 29 Pages

| |||

IDT72V3622/72V3632/72V3642 CMOS 3.3V SyncBiFIFOTM

256 x 36 x 2, 512 x 36 x 2, 1,024 x 36 x 2

COMMERCIAL TEMPERATURE RANGE

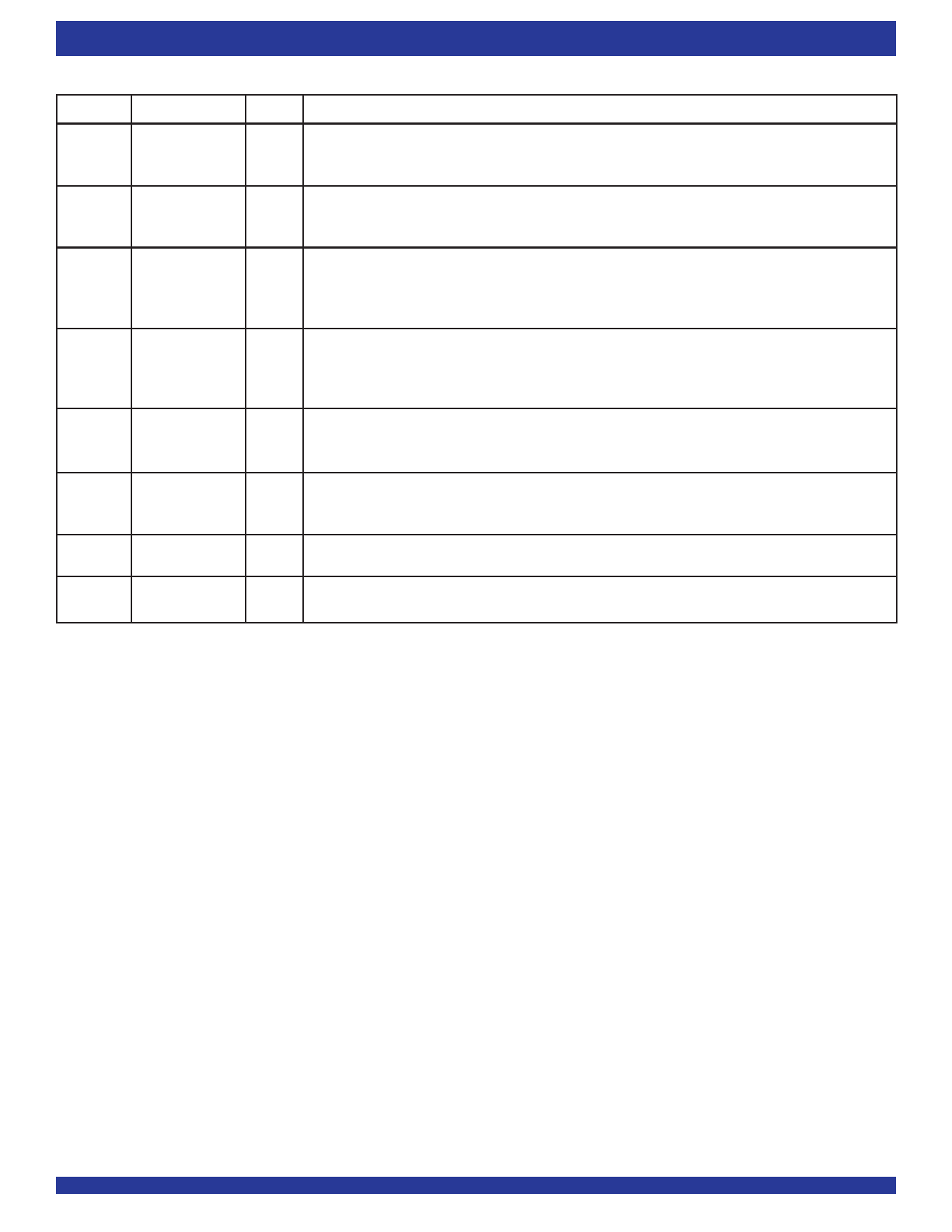

PIN DESCRIPTIONS (CONTINUED)

Symbol

Name

I/O

Description

MBA

Port A Mailbox

I

A HIGH level on MBA chooses a mailbox register for a port A read or write operation. When the

Select

A0-A35 outputs are active, a HIGH level on MBA selects data from the mail2 register for output and a

LOW level selects FIFO2 output register data for output.

MBB

Port B Mailbox

Select

I

A HIGH level on MBB chooses a mailbox register for a port B read or write operation. When the

B0-B35 outputs are active, a HIGH level on MBB selects data from the mail1 register or output and a

LOW level selects FIFO1 output register data for output.

MBF1

Mail1 Register

Flag

O

MBF1 is set LOW by a LOW-to-HIGH transition of CLKA that writes data to the mail1 register.

Writes to the mail1 register are inhibited while MBF1 is LOW. MBF1 is set HIGH by a LOW-to-HIGH

transition of CLKB when a port B read is selected and MBB is HIGH. MBF1 is set HIGH when FIFO1

is reset.

MBF2

Mail2 Register

Flag

O

MBF2 is set LOW by a LOW-to-HIGH transition of CLKB that writes data to the mail2 register. Writes

to the mail2 register are inhibited while MBF2 is LOW. MBF2 is set HIGH by a LOW-to-HIGH

transition of CLKA when a port A read is selected and MBA is HIGH. MBF2 is also set HIGH when

FIFO2 is reset.

RST1

FIFO1 Reset

I

To reset FIFO1, four LOW-to-HIGH transitions of CLKA and four LOW-to-HIGH transitions of CLKB must

occur while RST1 is LOW. The LOW-to-HIGH transition of RST1 latches the status of FS0 and FS1 for

AFA and AEB offset selection. FIFO1 must be reset upon power up before data is written to its RAM.

RST2

FIFO2 Reset

I

To reset FIFO2, four LOW-to-HIGH transitions of CLKA and four LOW-to-HIGH transitions of CLKB must

occur while RST2 is LOW. The LOW-to-HIGH transition of RST2 latches the status of FS0 and FS1 for

AFB and AEA offset selection. FIFO2 must be reset upon power up before data is written to its RAM.

W/RA

Port A Write/

Read Select

I

A HIGH selects a write operation and a LOW selects a read operation on port A for a LOW-to-HIGH

transition of CLKA. The A0-A35 outputs are in the HIGH impedance state when W/RA is HIGH.

W/RB

Port B Write/

Read Select

I

A LOW selects a write operation and a HIGH selects a read operation on port B for a LOW-to-HIGH

transition of CLKB. The B0-B35 outputs are in the HIGH impedance state when W/RB is LOW.

5