SL2305ZC-1HT Просмотр технического описания (PDF) - Silicon Laboratories

Номер в каталоге

Компоненты Описание

Список матч

SL2305ZC-1HT Datasheet PDF : 11 Pages

| |||

SL2305

Low Jitter and Skew 10 to 140 MHz Zero Delay Buffer (ZDB)

Key Features

• 10 to 140 MHz operating frequency range

• Low output clock jitter:

- 140 ps-max c-c-j at 66 MHz

• Low output-to-output skew: 150 ps-max

• Low product-to-product skew: 400 ps-max

• 3.3 V power supply range

• Low power dissipation:

- 14 mA-max at 66MHz

- 26 mA-max at 133 MHz

• One input drives 5 outputs organized as 4+1

• SpreadThru™ PLL that allows use of SSCG

• Standard and High-Drive options

• Available in 8-pin SOIC and TSSOP packages

• Available in Commercial and Industrial grades

Applications

• Printers and MFPs

• Digital Copiers

• PCs and Work Stations

• DTV

• Routers, Switchers and Servers

• Digital Embeded Systems

Description

The SL2305 is a low skew, low jitter and low power Zero

Delay Buffer (ZDB) designed to produce up to five (5) clock

outputs from one (1) reference input clock for high speed

clock distribution applications. The product has an on-chip

PLL which locks to the input clock at CLKIN and receives its

feedback internally from the CLKOUT pin.

The SL2305 is available with two (2) drive strength versions.

The -1 is the standard-drive version and -1H is the high-

drive version.

The SL2305 high-drive version operates up to 140MHz and

the standard drive version -1 operates up to 100.

The SL2305 enter into Power-Down (PD) mode if the input

at CLKIN is DC (0 to VDD). In this power-down state all five

(5) outputs are tri-stated and the PLL is turned off leading to

less than 12μA-max of power supply current draw.

Benefits

• Up to five (5) distribution of input clock

• Standard and High-Drive levels to control impedance

level, frequency range and EMI

• Low jitter and skew

• Low power dissipation

• Low cost

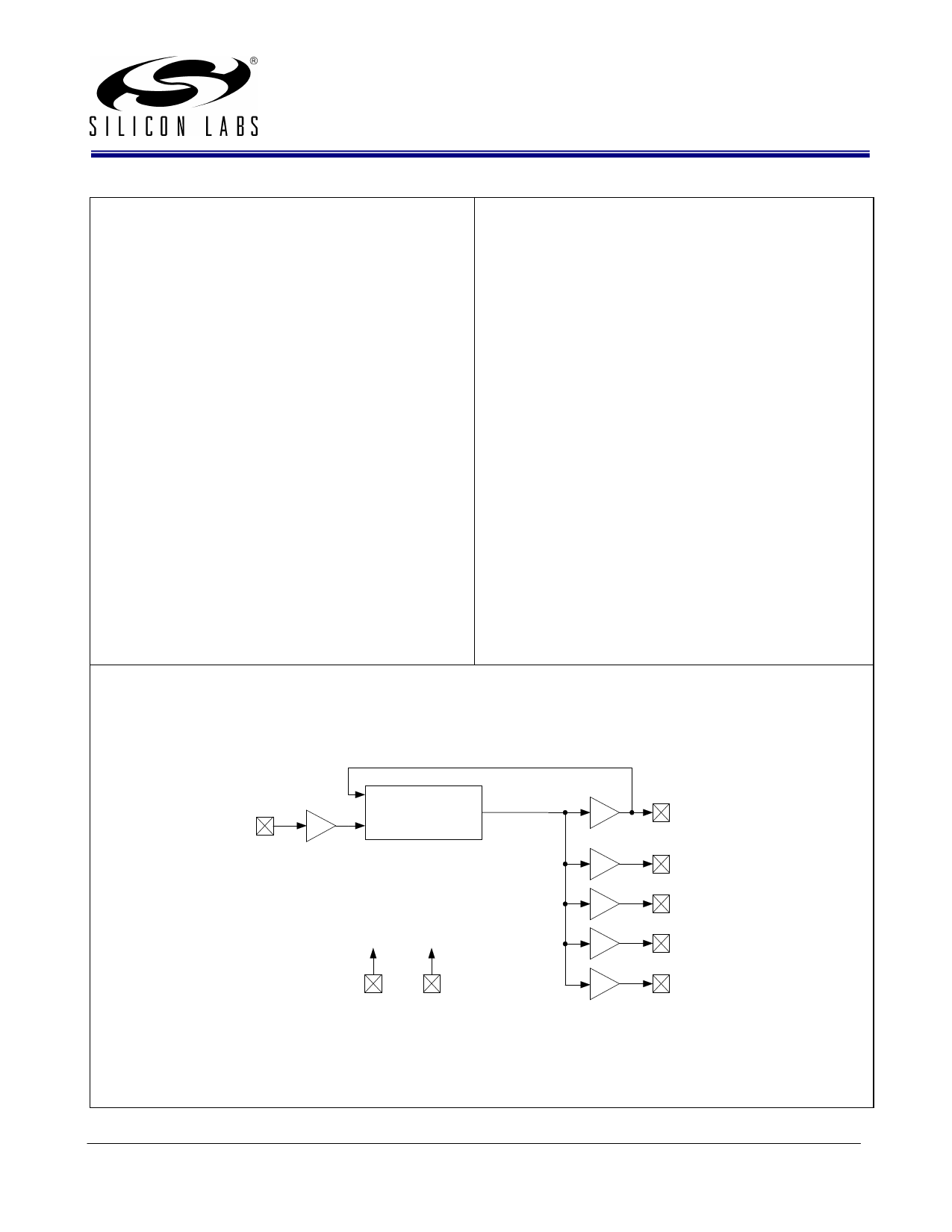

Block Diagram

PLL

CLKIN

VDD

GND

CLKOUT

CLK1

CLK2

CLK3

CLK4

Rev 2.1, October 22, 2007

400 West Cesar Chavez, Austin, TX 78701

1+(512) 416-8500

1+(512) 416-9669

Page 1 of 11

www.silabs.com