UL631H256 Просмотр технического описания (PDF) - Zentrum Mikroelektronik Dresden AG

Номер в каталоге

Компоненты Описание

Список матч

UL631H256 Datasheet PDF : 12 Pages

| |||

UL631H256

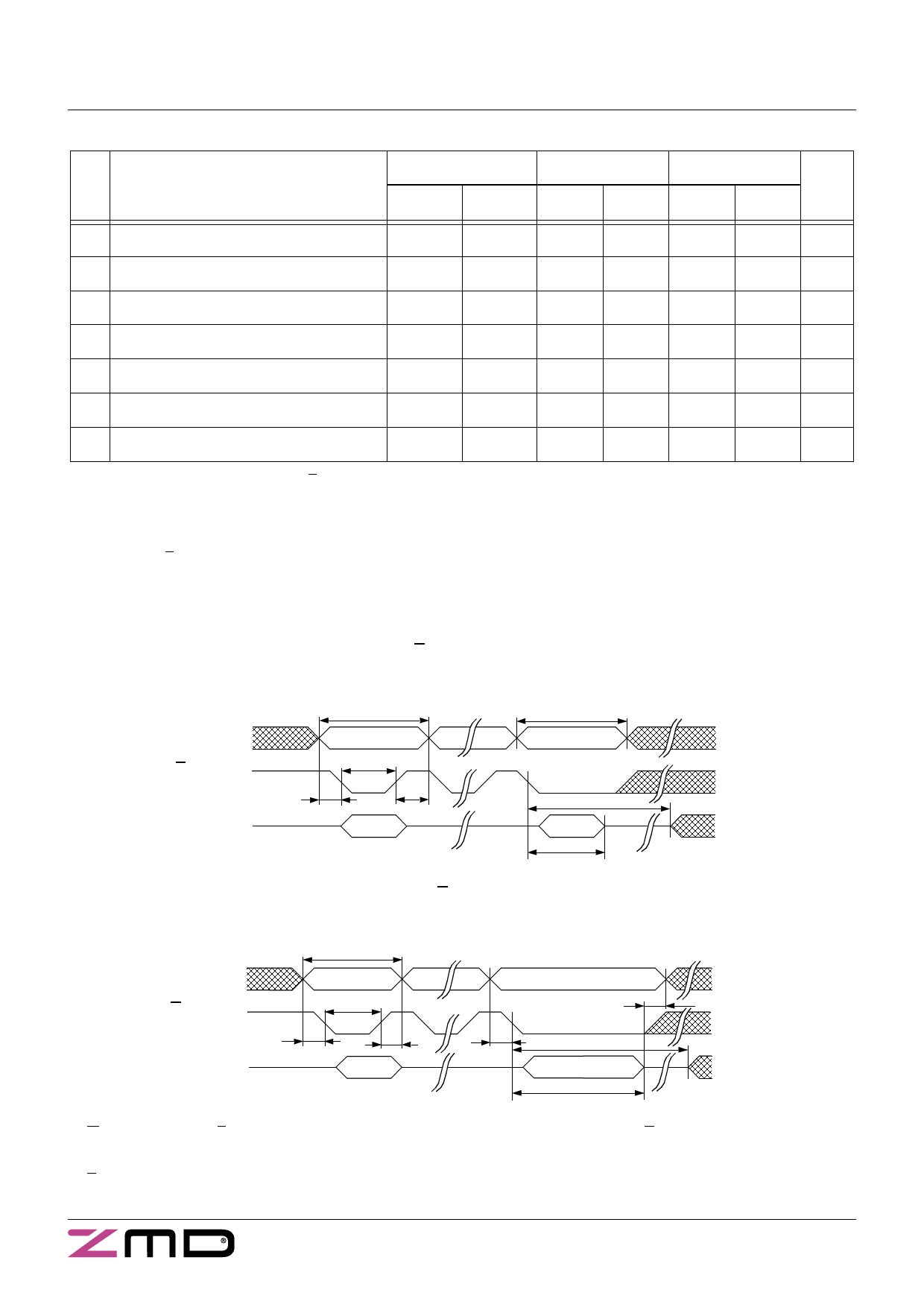

No. Software Controlled STORE/RECALL

Cyclel, n

Symbol

Alt.

IEC

35

Min.

Max.

45

Min.

Unit

Max.

25 STORE/RECALL Initiation Time

26 Chip Enable to Output Inactiveo

27 STORE Cycle Timep

28 RECALL Cycle Timeq

29 Address Setup to Chip Enabler

30 Chip Enable Pulse Widthr, s

31 Chip Disable to Address Changer

tAVAV

tcR

35

45

ns

tELQZ tdis(E)SR

600

600 ns

tELQXS

td(E)S

10

10

ms

tELQXR

td(E)R

20

20

ms

tAVELN tsu(A)SR

0

0

ns

tELEHN tw(E)SR

25

30

ns

tEHAXN th(A)SR

0

0

ns

n: The software sequence is clocked with E controlled READs

o: Once the software controlled STORE or RECALL cycle is initiated, it completes automatically, ignoring all inputs.

p: Note that STORE cycles (but not RECALL) are aborted by VCC < VSWITCH (STORE inhibit).

q: An automatic RECALL also takes place at power up, starting when VCC exceeds VSWITCH and takes tRESTORE. VCC must not drop below

VSWITCH once it has been exceeded for the RECALL to function properly.

r: Noise on the E pin may trigger multiple READ cycles from the same address and abort the address sequence.

s: If the Chip Enable Pulse Width is less than ta(E) (see Read Cycle) but greater than or equal tw(E)SR, than the data may not be valid at

the end of the low pulse, however the STORE or RECALL will still be initiated.

Software Controlled STORE/RECALL Cyclet, u (E = HIGH after STORE initiation)

Ai

E

DQi

Output

tcR (25)

ADDRESS 1

tw(E)SR

tsu(A)SR (29) (30) th(A)SR

(31)

High Impedance

VALID

tcR (25)

ADDRESS 6

td(E)S (27) td(E)R (28)

VALID

tdis(E)SR (26)

Software Controlled STORE/RECALL Cycler, s, t, u (E = LOW after STORE initiation)

Ai

E

DQi

Output

tcR (25)

ADDRESS 1

tsu(A)SR (29)

tw(E)SR

(30)

(31) th(A)SR

High Impedance

VALID

(29)

tsu(A)SR

ADDRESS 6

th(A)SR (31)

td(E)S (27)

td(E)R (28)

VALID

tdis(E)SR (26)

t: W must be HIGH when E is LOW during the address sequence in order to initiate a nonvolatile cycle. G may be either HIGH or LOW

throughout. Addresses 1 through 6 are found in the mode selection table. Address 6 determines wheter the UL631H256 performs a

STORE or RECALL.

u: E must be used to clock in the address sequence for the Software controlled STORE and RECALL cycles.

8

April 7, 2005