IDT72V36100_06 Просмотр технического описания (PDF) - Integrated Device Technology

Номер в каталоге

Компоненты Описание

Список матч

IDT72V36100_06 Datasheet PDF : 48 Pages

| |||

IDT72V36100/72V36110 3.3V HIGH DENSITY SUPERSYNC IITM 36-BIT FIFO

65,536 x 36 and 131,072 x 36

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

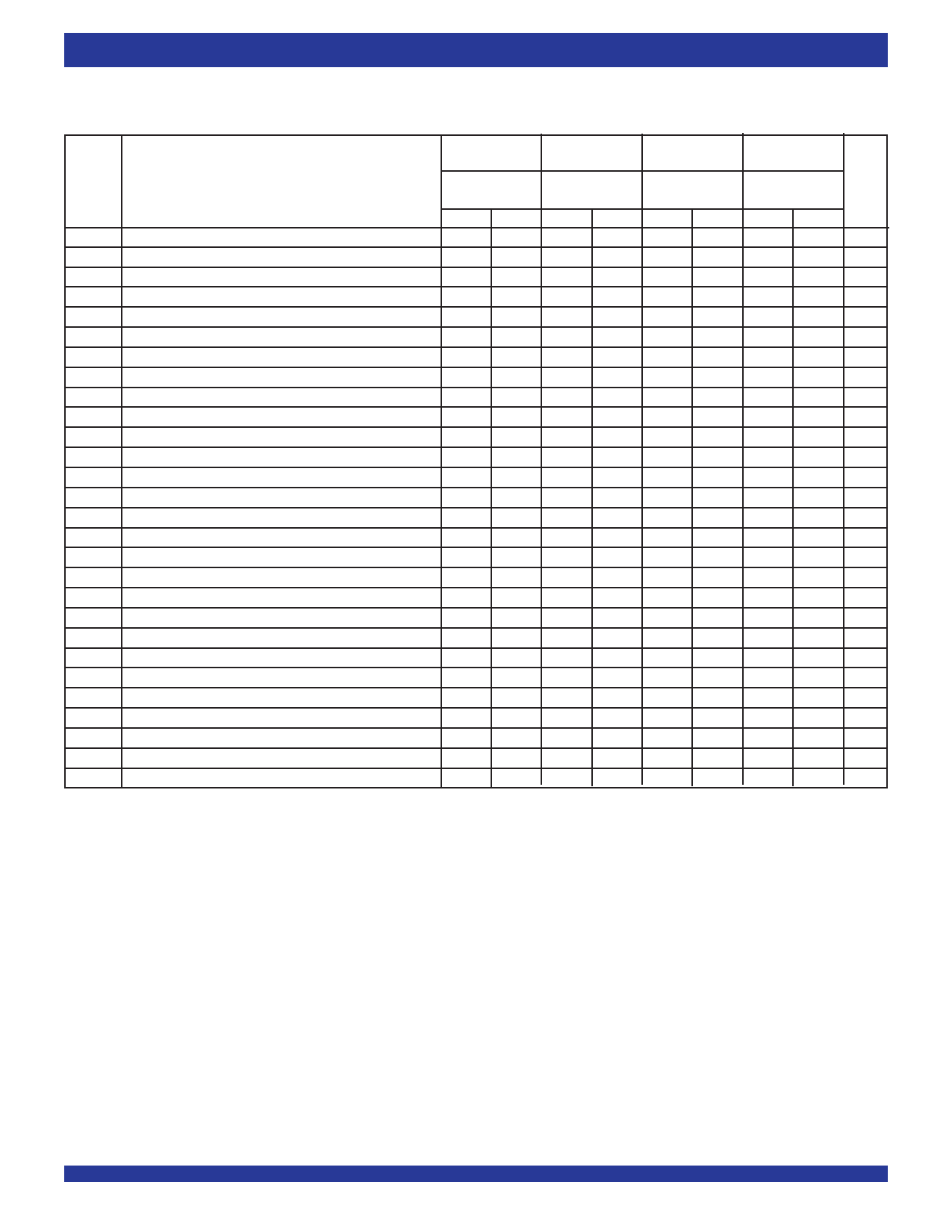

AC ELECTRICAL CHARACTERISTICS(1)

(Commercial: VCC = 3.3V ± 0.15V, TA = 0°C to +70°C; Industrial: VCC = 3.3V ± 0.15V, TA = -40°C to +85°C; JEDEC JESD8-A compliant)

Commercial Com’l & Ind’l(2)

PBGA & TQFP PBGA & TQFP

Commercial

TQFP Only

Com’l & Ind’l(2)

TQFP Only

IDT72V36100L6 IDT72V36100L7-5 IDT72V36100L10 IDT72V36100L15

IDT72V36110L6 IDT72V36110L7-5 IDT72V36110L10 IDT72V36110L15

Symbol

Parameter

fS

Clock Cycle Frequency

Min. Max. Min. Max. Min. Max. Min. Max. Unit

—

166

— 133.3 —

100 — 66.7 MHz

tA

Data Access Time(5)

1

4

1(5)

5

1(5)

6.5

1(5)

10

ns

tCLK

Clock Cycle Time

6

—

7.5

— 10

— 15

—

ns

tCLKH

Clock High Time

2.7

—

3.5

— 4.5

—

6

—

ns

tCLKL

Clock Low Time

2.7

—

3.5

— 4.5

—

6

—

ns

tDS

Data Setup Time

2

—

2.5

— 3.5

—

4

—

ns

tDH

Data Hold Time

0.5

—

0.5

— 0.5

—

1

—

ns

tENS

Enable Setup Time

2

—

2.5

— 3.5

—

4

—

ns

tENH

Enable Hold Time

0.5

—

0.5

— 0.5

—

1

—

ns

tLDS

Load Setup Time

3

—

3.5

— 3.5

—

4

—

ns

tLDH

Load Hold Time

0.5

—

0.5

— 0.5

—

1

—

ns

tRS

Reset Pulse Width(3)

10

—

10

— 10

— 15

—

ns

tRSS

Reset Setup Time

15

—

15

— 15

— 15

—

ns

tRSR

Reset Recovery Time

10

—

10

— 10

— 15

—

ns

tRSF

Reset to Flag and Output Time

—

15

—

15 —

15 —

15

ns

tRTS

Retransmit Setup Time

3

—

3.5

— 3.5

—

4

—

ns

tOLZ

Output Enable to Output in Low Z(4)

0

—

0

—

0

—

0

—

ns

tOE

Output Enable to Output Valid(5)

1

4

1(5)

6

1(5)

6

1(5)

8

ns

tOHZ

Output Enable to Output in High Z(4,5)

tWFF

Write Clock to FF or IR

1

4

1(5)

6

1(5)

6

1(5)

8

ns

—

4

—

5

—

6.5 —

10

ns

tREF

Read Clock to EF or OR

—

4

—

5

—

6.5 —

10

ns

tPAFA

Clock to Asynchronous Programmable Almost-Full Flag

—

10

— 12.5 —

16 —

20

ns

tPAFS Write Clock to Synchronous Programmable Almost-Full Flag

—

4

—

5

—

6.5 —

10

ns

tPAEA Clock to Asynchronous Programmable Almost-Empty Flag

—

10

— 12.5 —

16 —

20

ns

tPAES Read Clock to Synchronous Programmable Almost-Empty Flag —

4

—

5

—

6.5 —

10

ns

tHF

Clock to HF

—

10

— 12.5 —

16 —

20

ns

tSKEW1 Skew time between RCLK and WCLK for EF/OR and FF/IR

4

—

5

—

7

—

9

—

ns

tSKEW2 Skew time between RCLK and WCLK for PAE and PAF

5

—

7

— 10

— 14

—

ns

NOTES:

1. All AC timings apply to both Standard IDT mode and First Word Fall Through mode.

2. Industrial temperature range product for the 7-5ns and 15ns are available as a standard device. All other speed grades are available by special order.

3. Pulse widths less than minimum values are not allowed.

4. Values guaranteed by design, not currently tested.

5. TQFP package only: for speed grades 7-5ns, 10ns and 15ns the minimum for tA, tOE, and tOHZ is 2ns.

9

APRIL 6, 2006