L9822E(2002) Просмотр технического описания (PDF) - STMicroelectronics

Номер в каталоге

Компоненты Описание

Список матч

L9822E Datasheet PDF : 10 Pages

| |||

L9822E

pin), allowing the other SPI devices to be cascaded

in a daisy chain with the L9822ESP.

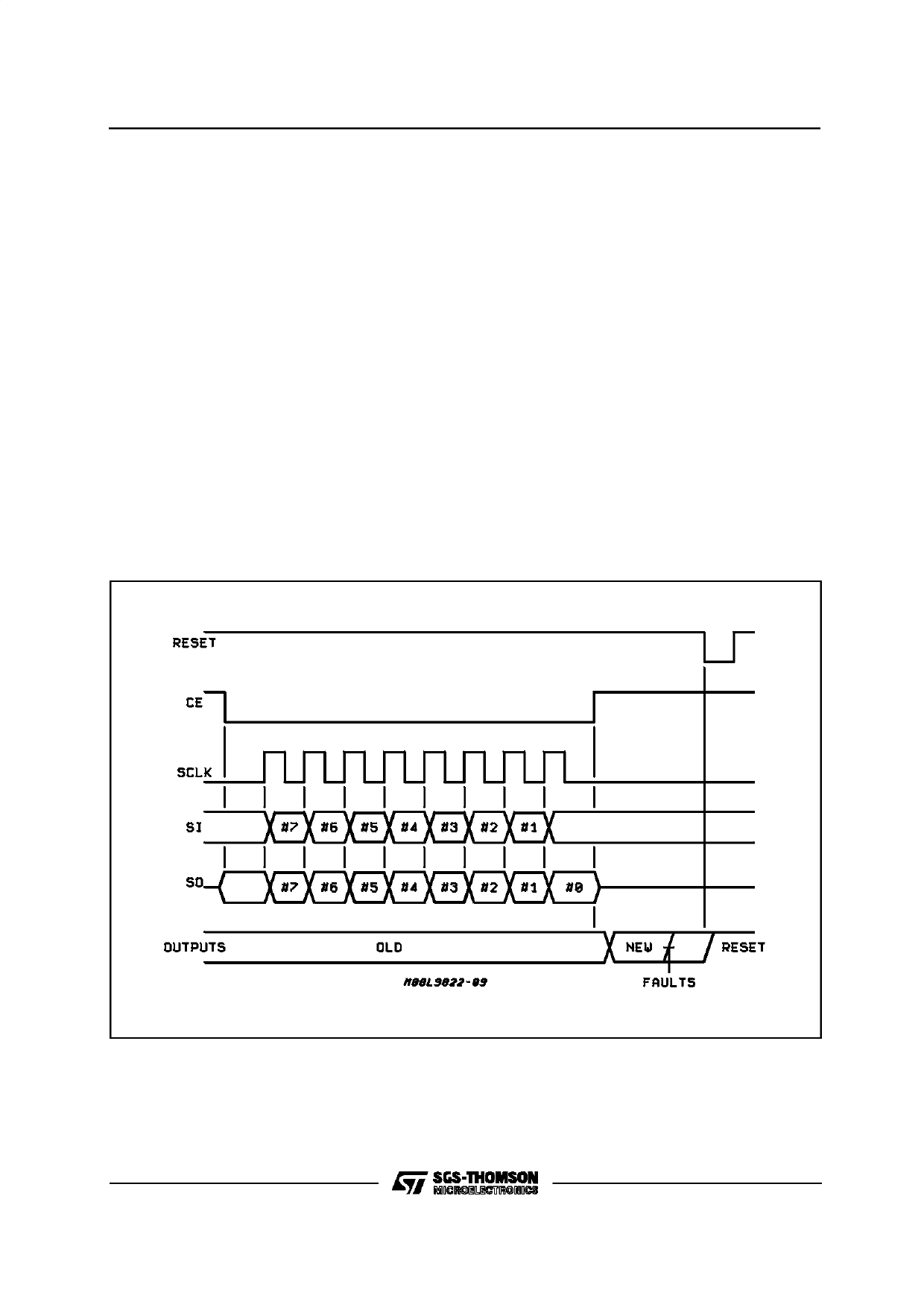

CE Low to High Transition

Once the last data bit has been shifted into the

L9822ESP, the CE pin should be pulled high.

At the rising edge of CE the shift register data is

latched into the parallel latch and the output stages

will be actuated by the new data. An internal 160µs

delay timer will also be started at this rising edge

(see tUD). During the 160µs period, the outputs will

be protected only by the analog current limiting cir-

cuits since the resetting of the parallel latches by

faults conditions will be inhibited during this period.

This allows the part to overcome any high inrush cur-

rents that may flow immediately after turn on. Once

the delay period has elapsed, the output voltages

are sensed by the comparators and any output with

voltages higher than 1.8V are latched OFF. It should

be noted that the SCLK pin should be low at both

transitions of the CE pin to avoid any false clocking

of the shift register. The SCLK input is gated by the

CE pin, so that the SCLK pin is ignored whenever

the CE pin is high.

FAULT CONDITIONS CHECK

Checking for fault conditions may be done in the fol-

lowing way. Clock in a new control byte. Wait 160

microseconds or so to allow the outputs to settle.

Clock in the same control byte and observe the diag-

nostic data that comes out of the device. The diag-

nostic bits should be identical to the bits that were

first clocked in. Any differences would point to a fault

on that output. If the output was programmed ON by

clocking in a zero, and a one came back as the di-

agnostic bit for that output, the output pin was still

high and a short circuit or overload condition exists.

If the output was programmed OFF by clocking in a

one, and a zero came back as the diagnostic bit for

that output, nothing had pulled the output pin high

and it must be floating, so an open circuit condition

exists for that output.

Figure 1 : Byte Timing with Asynchronous Reset.

6/10