CS5342_06 Просмотр технического описания (PDF) - Cirrus Logic

Номер в каталоге

Компоненты Описание

Список матч

CS5342_06 Datasheet PDF : 21 Pages

| |||

CS5342

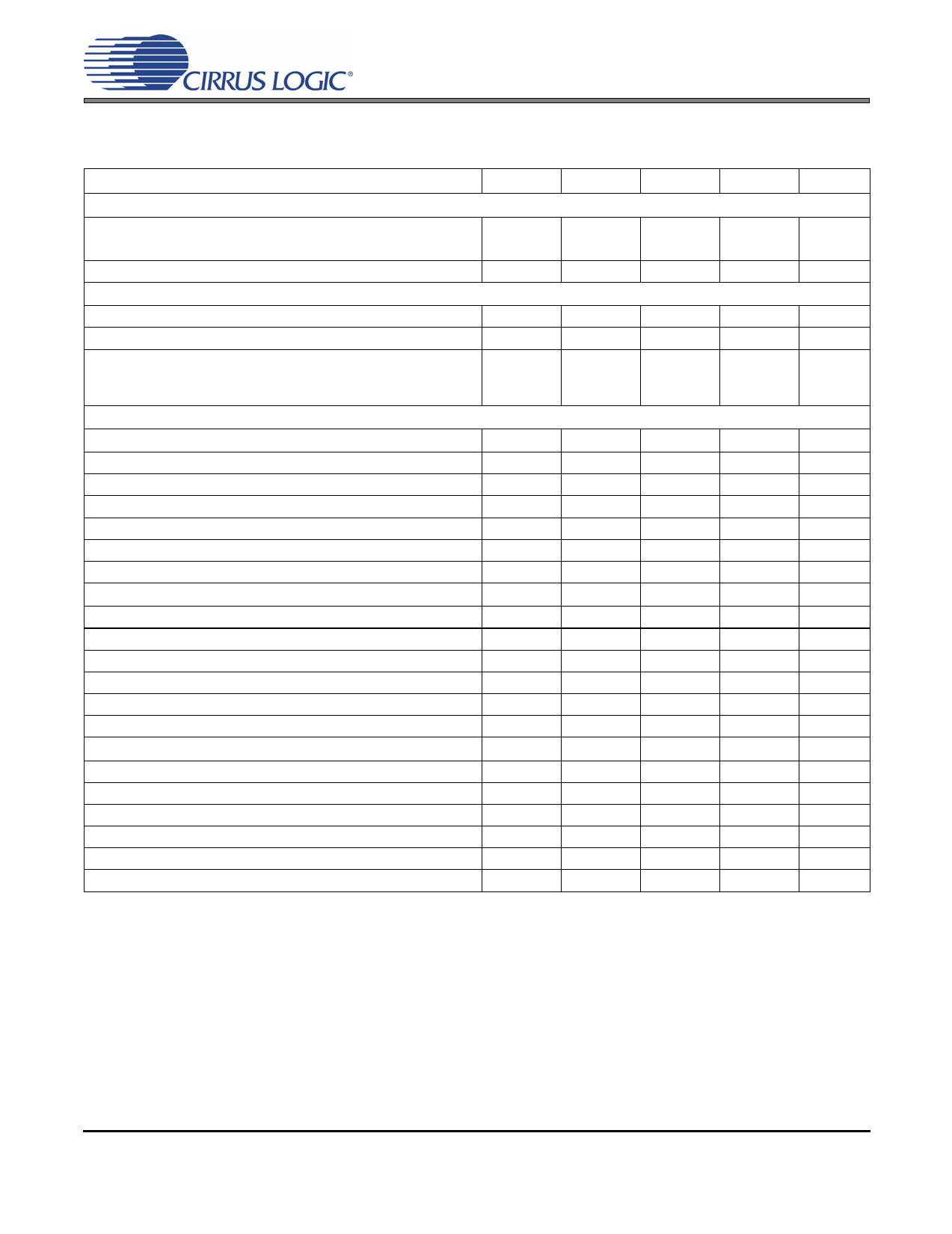

SWITCHING CHARACTERISTICS - SERIAL AUDIO PORT

(Logic "0" = GND = 0 V; Logic "1" = VL, CL = 20 pF)

Parameter

MCLK Specifications

MCLK Period

MCLK Pulse Duty Cycle

Master Mode

SCLK falling to LRCK

SCLK falling to SDOUT valid

SCLK Duty Cycle

Slave Mode

Single-Speed (Note 10)

LRCK Duty Cycle

SCLK Period

SCLK Duty Cycle

SDOUT valid before SCLK rising

SDOUT valid after SCLK rising

SCLK falling to LRCK edge

Double-Speed (Note 10)

LRCK Duty Cycle

SCLK Period (Note 11)

SCLK Duty Cycle

SDOUT valid before SCLK rising

SDOUT valid after SCLK rising

SCLK falling to LRCK edge

Quad-Speed (Note 10)

LRCK Duty Cycle

SCLK Period (Note 11)

SCLK Duty Cycle

SDOUT valid before SCLK rising

SDOUT valid after SCLK rising

SCLK falling to LRCK edge

Symbol Min

Typ

tclkw

26

-

52

-

40

-

tmslr

-20

-

tsdo

-

-

Single-Speed

-

50

Double-Speed

-

50

Quad-Speed

-

33

40

-

tsclkw

313

-

45

-

tstp

10

-

thld

5

-

tslrd

-20

-

40

-

tsclkw

208

-

45

-

tstp

10

-

thld

5

-

tslrd

-20

-

40

-

tsclkw

104

-

40

-

tstp

10

-

thld

5

-

tslrd

-8

-

Max

30

1302

60

20

32

-

-

-

Unit

ns

ns

%

ns

ns

%

%

%

60

%

-

ns

55

%

-

ns

-

ns

20

ns

60

%

-

ns

55

%

-

ns

-

ns

20

ns

60

%

-

ns

50

%

-

ns

-

ns

8

ns

10. For a description of speed modes, please refer to Table 1 on page 14

11. SCLK must be derived synchronously from MCLK and the ratio of SCLK/LRCK must be equal to 48.

10

DS608F1