CS5505(2009) Просмотр технического описания (PDF) - Cirrus Logic

Номер в каталоге

Компоненты Описание

Список матч

CS5505 Datasheet PDF : 40 Pages

| |||

CS5505/6/7/8

CS5505/6/7/8

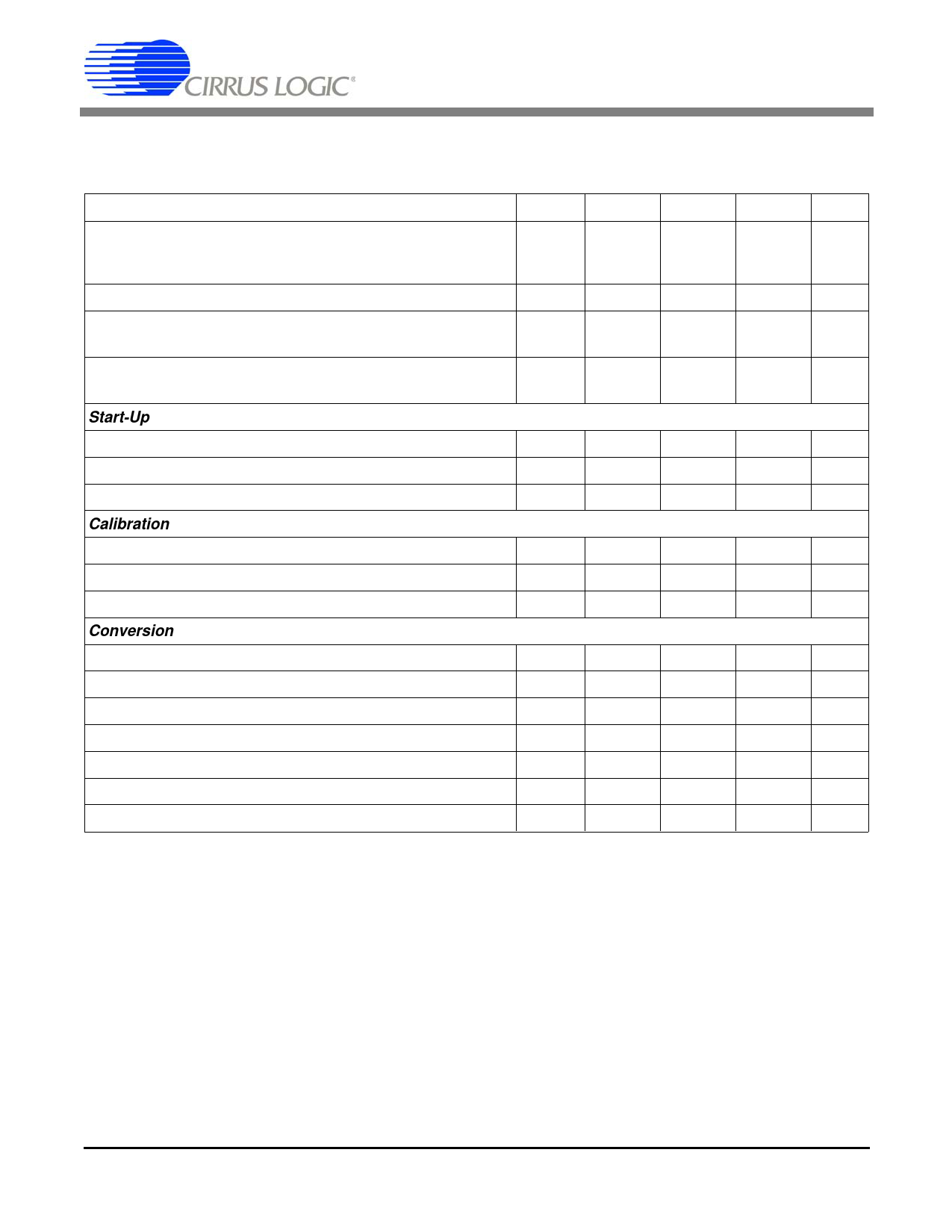

5V SWITCHING CHARACTERISTICS (TA = TMIN to TMAX; VA+, VD+ = 5V ± 10%;

VA- = -5V ± 10%; Input Levels: Logic 0 = 0V, Logic 1 = VD+; CL = 50 pF.) (Note 2)

Parameter

Symbol Min

Typ

Max Units

Master Clock Frequency:

Master Clock Duty Cycle

Internal Oscillator:

External Clock:

-A,B XIN

-S or

fclk

30.0 32.768 53.0 kHz

30.0 32.768 34.0 kHz

30

-

163 kHz

40

-

60

%

Rise Times:

Any Digital Input (Note 10) trise

-

Any Digital Output

-

-

1.0

µs

50

-

ns

Fall Times:

Start-Up

Any Digital Input (Note 10) tfall

-

Any Digital Output

-

-

1.0

µs

20

-

ns

Power-On Reset Period

(Note 11) tres

-

10

-

ms

Oscillator Start-up Time

XTAL=32.768 kHz (Note 12) tosu

-

500

-

ms

Wake-up Period

(Note 13) twup

-

1800/fclk

-

s

Calibration

CONV Pulse Width (CAL = 1)

(Note 14) tccw

100

-

-

ns

CONV and CAL High to Start of Calibration

tscl

-

-

2/fclk+200 ns

Start of Calibration to End of Calibration

tcal

-

3246/fclk

-

s

Conversion

Set Up Time

A0, A1 to CONV High

tsac

50

-

-

ns

Hold Time

A0, A1 after CONV High

thca

100

-

-

ns

CONV Pulse Width

tcpw

100

-

-

ns

CONV High to Start of Conversion

tscn

-

-

2/fclk+200 ns

Set Up Time

BP/UP stable prior to DRDY fal ling tbus 82/fclk

-

-

s

Hold Time

BP/UP stable after DRDY fal ls tbuh

0

-

-

ns

Start of Conversion to End of Conversion

(Note 15) tcon

-

1624/fclk

-

s

Notes: 10. Specified using 10% and 90% points on waveform of interest.

11. An internal power-on-reset is activated whenever power is applied to the device, or when coming out

of a SLEEP state.

12. Oscillator start-up time var ies with the crystal parameters. This specification does not apply when

using an external clock source.

13. The wake-up period begins once the oscillator starts;

or when using an external fclk, after the power-on reset time elapses.

14. Calibration can also be initiated by pulsing CAL high while CONV=1.

15. Conversion time will be 1622/fclk if CONV remains high continuously.

66

DS59F7