AT76C101 Просмотр технического описания (PDF) - Atmel Corporation

Номер в каталоге

Компоненты Описание

Список матч

AT76C101 Datasheet PDF : 13 Pages

| |||

AT76C101

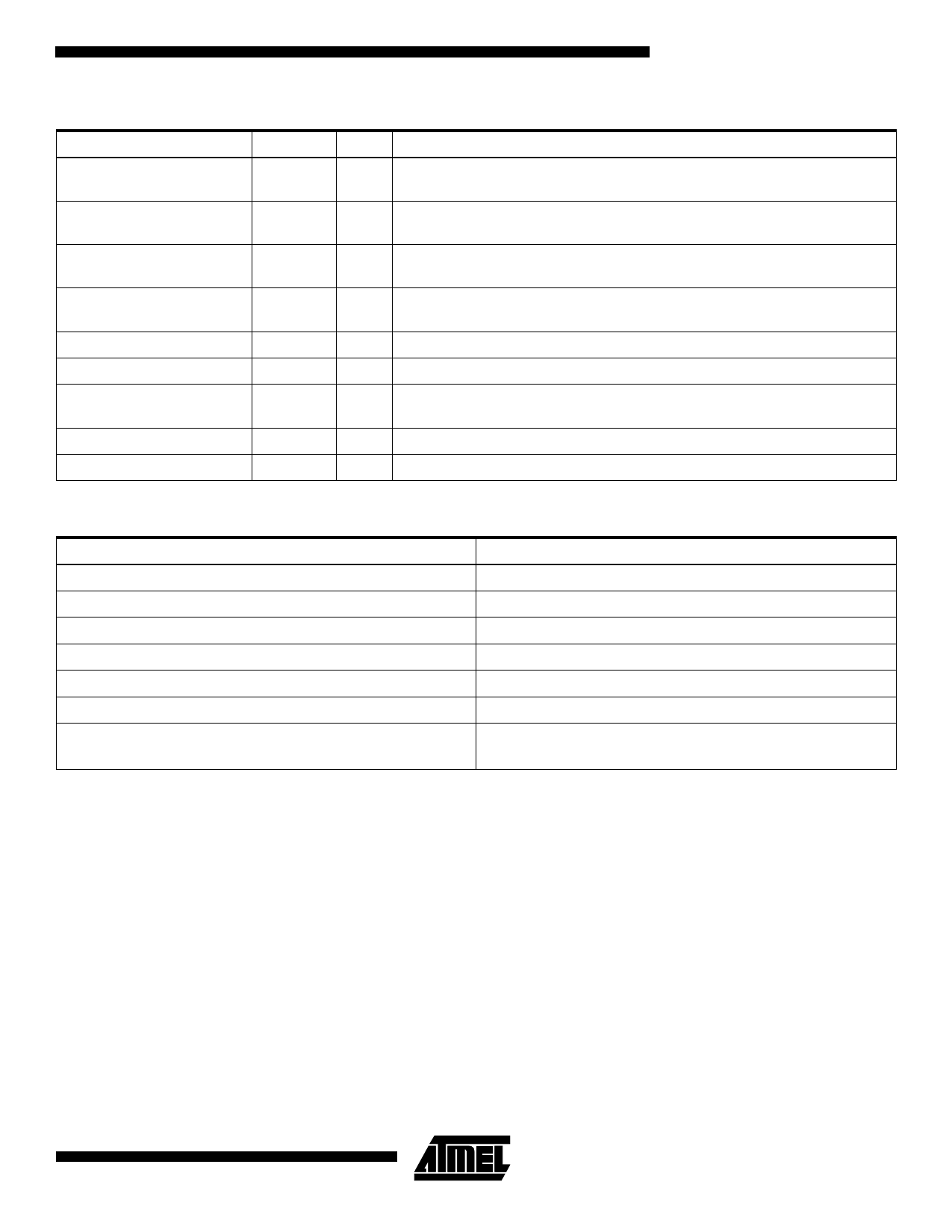

Table 2. Register File Description

Register

Address

FIFO_Status

0F817

Write_Cnt_Reg

0F818

Read_Cnt_Reg

0F819

Mem_Start_Addr_Low

0F81A

Mem_Start_Addr_Med

Mem_Start_Addr_High

Mem_End_Addr_Low

0F81B

0F81C

0F81D

Mem_End_Addr_Med

Mem_End_Addr_High

0F81E

0F81F

R/W Description

R Shows the status of the internal FIFO. Bit 0 is the FIFO full indicator and bit 1 is

the FIFO empty indicator.

R/W The number of wait states required during a write to external memory is

programmed into this register.

R/W The number of wait states required during a read from external memory is

programmed into this register.

R/W Mem_Start_Addr - low byte. The external memory start address is

programmed here.

R/W Mem_Start_Adrr - middle byte (bit 16 to 31)

R/W Mem_Start_Addr - high byte (bit 32 to 39)

R Mem_End_Addr - low byte. AT76C101 writes the address of the last byte of the

frame written into the external memory.

R Mem_End_Addr - middle byte (bit 16 to 31).

R Mem_End_Addr - high byte (bit 32 to 39).

Table 3. Internal Memory Addressing

Module

Quantization Tables (256 x 16 bits)

DC Huffman Tables (32 x 28 bits)

AC Huffman Tables (512 x 28 bits)

Maxmin Tables - For Decoding only (64 x 40 bits)

Pixel Buffer (4 buffers of size 128 x 8 bits each)

DCT Coefficient Buffer (2 buffers of size 64 x 16 each)

Compressed Data FIFO (64 x 8 bits)

Address Range

0x00000-0x001FF

0x01000-0x0107F

0x03000-0x031FF

0x04000-0x04200

0x04000-0x04200

0x05000-0x050FF

Write Port 0x06000-0x06040

Read Port 0x07000-0x07040

11