M38B57MFH-XXXXFP Просмотр технического описания (PDF) - MITSUBISHI ELECTRIC

Номер в каталоге

Компоненты Описание

Список матч

M38B57MFH-XXXXFP Datasheet PDF : 355 Pages

| |||

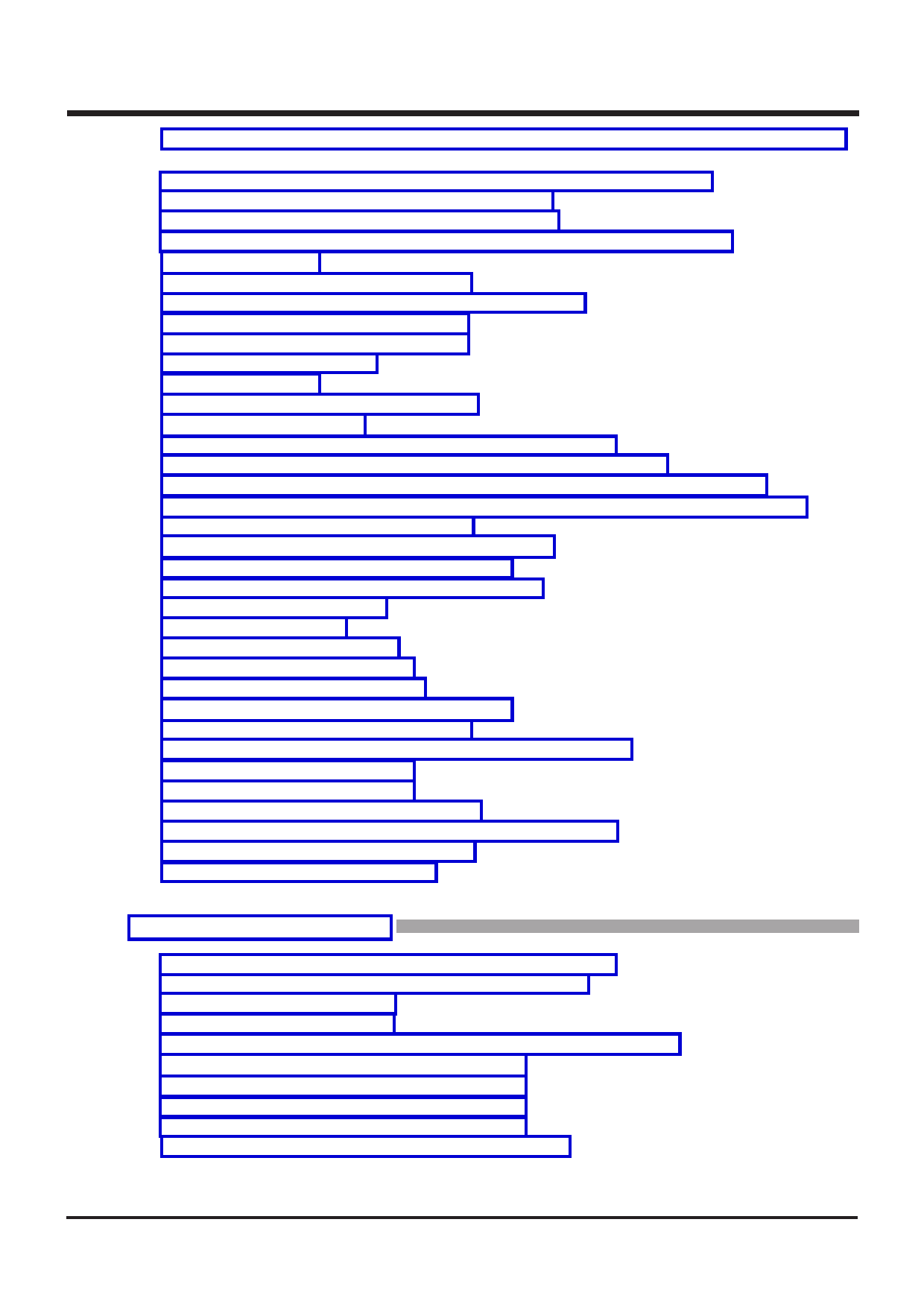

List of figures

Fig. 46 Example of using FLD automatic display RAM in 16-timing•gradation display mode

........................................................................................................................................................ 1-45

Fig. 47 Example of using FLD automatic display RAM in 32-timing mode ......................... 1-46

Fig. 48 Structure of FLDRAM write disable register ............................................................... 1-47

Fig. 49 Example of digit timing using grid scan type ............................................................. 1-48

Fig. 50 Example of using FLD automatic display RAM using grid scan type .................... 1-48

Fig. 51 FLDC timing .................................................................................................................... 1-50

Fig. 52 P84 to P87 FLD output waveform ................................................................................. 1-51

Fig. 53 Structure of port P8 FLD output control register ....................................................... 1-51

Fig. 54 Structure of A-D control register .................................................................................. 1-52

Fig. 55 Black diagram of A-D converter ................................................................................... 1-52

Fig. 56 PWM block diagram ....................................................................................................... 1-53

Fig. 57 PWM timing ..................................................................................................................... 1-54

Fig. 58 Structure of PWM control register ............................................................................... 1-55

Fig. 59 14-bit PWM timing .......................................................................................................... 1-55

Fig. 60 Interrupt interval determination circuit block diagram ............................................... 1-56

Fig. 61 Structure of itnerrupt interval determination control register .................................... 1-57

Fig. 62 Interrupt inteval determination operation example (at rising edge active) ............. 1-57

Fig. 63 Interrupt interval determination operation example (at both-sided edge active) ... 1-57

Fig. 64 Block diagram of watchdog timer ................................................................................. 1-58

Fig. 65 Structure of watchdog timer control register .............................................................. 1-58

Fig. 66 Block diagram of buzzer output circuit ........................................................................ 1-59

Fig. 67 Structure of buzzer output control register ................................................................ 1-59

Fig. 68 Reset circuit example .................................................................................................... 1-60

Fig. 69 Reset sequence .............................................................................................................. 1-60

Fig. 70 Internal status at reset .................................................................................................. 1-61

Fig. 71 Ceramic resonator circuit .............................................................................................. 1-62

Fig. 72 External clock input circuit ............................................................................................ 1-62

Fig. 73 Clock generating circuit block diagram ....................................................................... 1-63

Fig. 74 State transitions of system clock ................................................................................. 1-64

Fig. 75 Programming and testing of One Time PROM version ............................................ 1-66

Fig. 76 Digit timing waveform (1) .............................................................................................. 1-67

Fig. 77 Digit timing waveform (2) .............................................................................................. 1-68

Fig. 78 Timing chart after interrupt occurs ............................................................................... 1-70

Fig. 79 TIme up to execution of interrupt processing routine ............................................... 1-70

Fig. 80 A-D conversion equivalent circuit ................................................................................. 1-72

Fig. 81 A-D conversion timing chart.......................................................................................... 1-72

CHAPTER 2 APPLICATION

Fig. 2.1.1 Memory assignment of I/O port relevant registers .................................................. 2-2

Fig. 2.1.2 Structure of port Pi (i = 0, 1, 2, 3, 4, 5, 7, 8) ........................................................ 2-3

Fig. 2.1.3 Structure of port P6 ..................................................................................................... 2-3

Fig. 2.1.4 Structure of port P9 ..................................................................................................... 2-3

Fig. 2.1.5 Structure of port Pi (i = 0, 2, 4, 5, 7, 8) direction register ................................... 2-4

Fig. 2.1.6 Structure of port P6 direction register ...................................................................... 2-4

Fig. 2.1.7 Structure of port P9 direction register ...................................................................... 2-5

Fig. 2.1.8 Structure of pull-up control register 1 ....................................................................... 2-5

Fig. 2.1.9 Structure of pull-up control register 2 ....................................................................... 2-6

Fig. 2.2.1 Memory map of registers relevant to timers .......................................................... 2-10

ii

38B5 Group User’s Manual