W48S87-72X Просмотр технического описания (PDF) - Cypress Semiconductor

Номер в каталоге

Компоненты Описание

Список матч

W48S87-72X Datasheet PDF : 19 Pages

| |||

W48S87-72

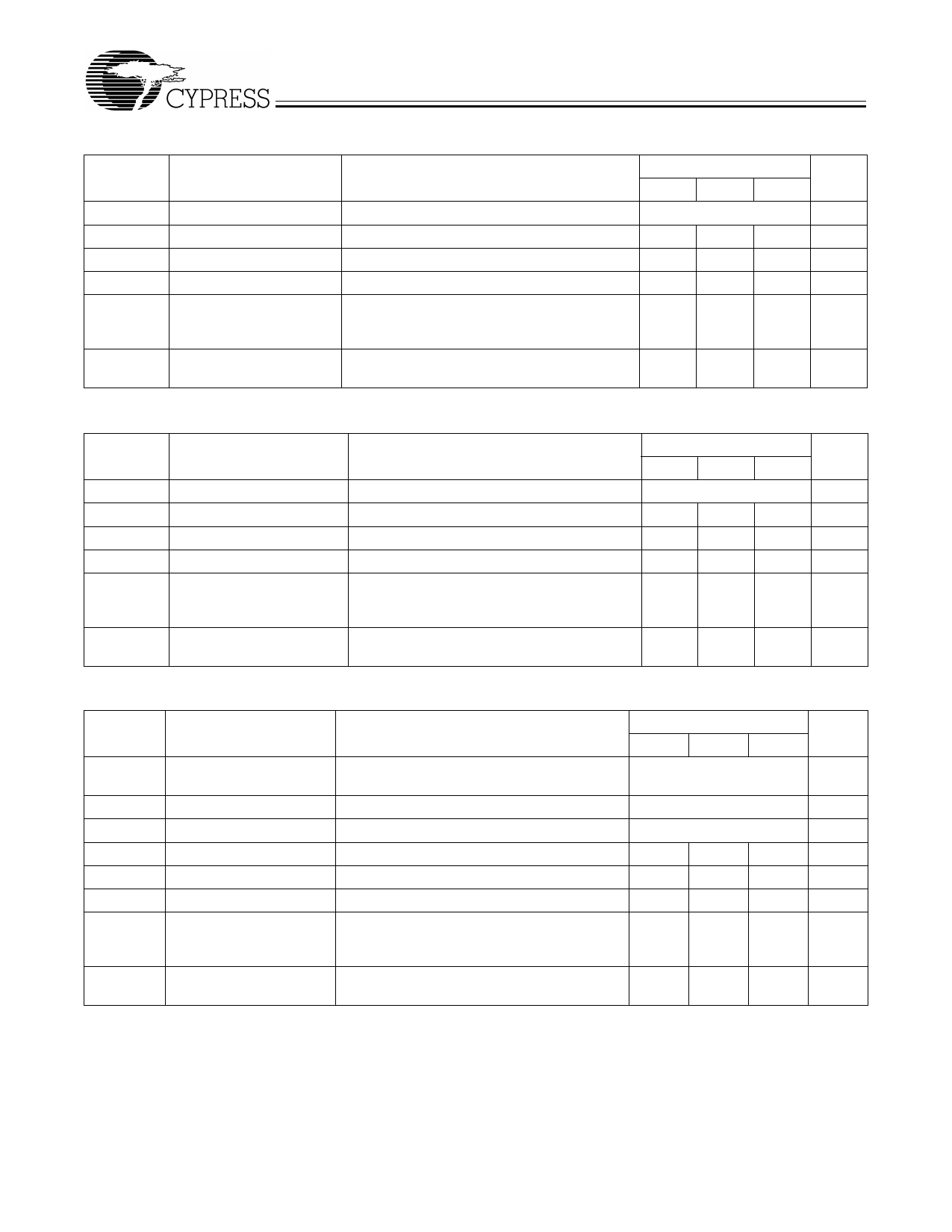

REF0 Clock Output (Lump Capacitance Test Load = 45 pF)

Parameter

Description

Test Condition/Comments

f

Frequency, Actual

Frequency generated by crystal oscillator

tR

Output Rise Edge Rate Measured from 0.4V to 2.4V

tF

Output Fall Edge Rate Measured from 2.4V to 0.4V

tD

Duty Cycle

Measured on rising and falling edge at 1.5V

fST

Frequency Stabilization Assumes full supply voltage reached within

from Power-up (cold start) 1 ms from power-up. Short cycles exist prior to

frequency stabilization.

Zo

AC Output Impedance Average value during switching transition.

Used for determining series termination value.

CPU = 60/66.8 MHz

Min. Typ. Max.

14.31818

1

4

1

4

45

50

55

1.5

16

Unit

MHz

V/ns

V/ns

%

ms

Ω

REF1 Clock Output (Lump Capacitance Test Load = 20 pF)

Parameter

Description

f

Frequency, Actual

tR

Output Rise Edge Rate

tF

Output Fall Edge Rate

tD

Duty Cycle

fST

Frequency Stabilization

from Power-up (cold start)

Zo

AC Output Impedance

Test Condition/Comments

Frequency generated by crystal oscillator

Measured on rising and falling edge at 1.5V

Assumes full supply voltage reached within

1 ms from power-up. Short cycles exist prior to

frequency stabilization.

Average value during switching transition.

Used for determining series termination value.

CPU = 60/66.8 MHz

Min. Typ. Max.

14.31818

0.5

2

0.5

2

45

55

1.5

40

Unit

MHz

V/ns

V/ns

%

ms

Ω

48/24MHZ Clock Outputs (Lump Capacitance Test Load = 20 pF)

Parameter

Description

Test Condition/Comments

f

Frequency, Actual

Determined by PLL divider ratio

(see n/m below)

fD

Deviation from 48 MHz (48.008 – 48)/48

m/n

PLL Ratio

(14.31818 MHz x 57/17 = 48.008 MHz)

tR

Output Rise Edge Rate

tF

Output Fall Edge Rate

tD

Duty Cycle

Measured on rising and falling edge at 1.5V

fST

Frequency Stabilization Assumes full supply voltage reached within

from Power-up (cold start) 1 ms from power-up. Short cycles exist prior to

frequency stabilization.

Zo

AC Output Impedance Average value during switching transition.

Used for determining series termination value.

CPU = 60/66.8 MHz

Min. Typ. Max.

48.008/24.004

+167

57/17

0.5

2

0.5

2

45

50

55

3

40

Unit

MHz

ppm

V/ns

V/ns

%

ms

Ω

16