IDT723622L30PF Просмотр технического описания (PDF) - Integrated Device Technology

Номер в каталоге

Компоненты Описание

Список матч

IDT723622L30PF Datasheet PDF : 26 Pages

| |||

IDT723622/723632/723642 CMOS SyncBiFIFO™

256 x 36 x 2, 512 x 36 x 2, 1024 x 36 x 2

COMMERCIAL TEMPERATURE RANGE

SIGNAL DESCRIPTION

RESET

The FIFO memories of the IDT723622/723632/723642

are reset separately by taking their reset (RST1, RST2) inputs

LOW for at least four port-A clock (CLKA) and four port-B clock

(CLKB) LOW-to-HIGH transitions. The reset inputs can switch

asynchronously to the clocks. A FIFO reset initializes the

internal read and write pointers and forces the input-ready flag

(IRA, IRB) LOW, the output-ready flag (ORA, ORB) LOW, the

almost-empty flag (AEA, AEB) LOW, and the almost-full flag

(AFA, AFB) HIGH. Resetting a FIFO also forces the mailbox

flag (MBF1, MBF2) of the parallel mailbox register HIGH. After

a FlFO is reset, its input-ready flag is set HIGH after two clock

cycles to begin normal operation. A FIFO must be reset after

power up before data is written to its memory.

A LOW-to HIGH transition on a FlFO reset (RST1, RST2)

input latches the value of the flag-select (FS0, FS1) inputs for

choosing the almost-full and almost-empty offset program-

ming method (see almost-empty and almost-full flag offset

programming below).

ALMOST-EMPTY FLAG AND ALMOST-FULL FLAG OFF-

SET PROGRAMMING

Four registers in the IDT723622/723632/723642 are used

to hold the offset values for the almost-empty and almost-full

flags. The port-B almost-empty flag (AEB) offset register is

labeled X1 and the port-A almost-empty flag (AEA) offset

register is labeled X2. The port-A almost-full flag (AFA) offset

register is labeled Y1 and the port-B almost-full flag (AFB)

offset register is labeled Y2. The index of each register name

corresponds to its FIFO number. The offset registers can be

loaded with preset values during the reset of a FIFO or they

can be programmed from port A (see Table 1 ) .

To load a FIFO almost-empty flag and almost-full flag

offset registers with one of the three preset values listed in

Table1, at least one of the flag-select inputs must be HIGH

during the LOW-to-HIGH transition of its reset input. For

example, to load the preset value of 64 into X1 and Y1, FS0

and FS1 must be HIGH when FlFO1 reset (RST1) returns

HIGH. Flag-offset registers associated with FIFO2 are loaded

with one of the preset values in the same way with FIFO2 reset

(RST2). When using one of the preset values for the flag

offsets, the FlFOs can be reset simultaneously or at different

times.

To program the X1, X2, Y1, and Y2 registers from port A,

both FlFOs should be reset simultaneously with FS0 and FS1

LOW during the LOW-to-HIGH transition of the reset inputs.

After this reset is complete, the first four writes to FIFO1 do not

store data in RAM but load the offset registers in the order Y1,

X1, Y2, X2. The port A data inputs used by the offset registers

are (A7-A0), (A8-A0), or (A9-A0) for the IDT723622,

IDT723632, or IDT723642, respectively. The highest num-

bered input is used as the most significant bit of the binary

number in each case. Valid programming values for the

registers ranges from 1 to 252 for the IDT723622; 1 to 508 for

the IDT723632; and 1 to 1020 for the IDT723642. After all the

offset registers are programmed from port A, the port-B input-

ready flag (IRB) is set HIGH, and both FIFOs begin normal

operation.

FIFO WRITE/READ OPERATION

The state of the port-A data (A0-A35) outputs is controlled

by port-A chip select (CSA) and port-A write/read select (W/

RA). The A0-A35 outputs are in the High-impedance state

when either CSA or W/RA is HIGH. The A0-A35 outputs are

active when both CSA and W/RA are LOW.

Data is loaded into FIFO1 from the A0-A35 inputs on a

LOW-to-HIGH transition of CLKA when CSA is LOW, W/RA is

HIGH, ENA is HIGH , MBA is LOW, and IRA is HIGH. Data is

read from FIFO2 to the A0-A35 outputs by a LOW-to-HIGH

transition of CLKA when CSA is LOW, W/RA is LOW, ENA is

HIGH, MBA is LOW, and ORA is HIGH (see Table 2). FIFO

reads and writes on port A are independent of any concurrent

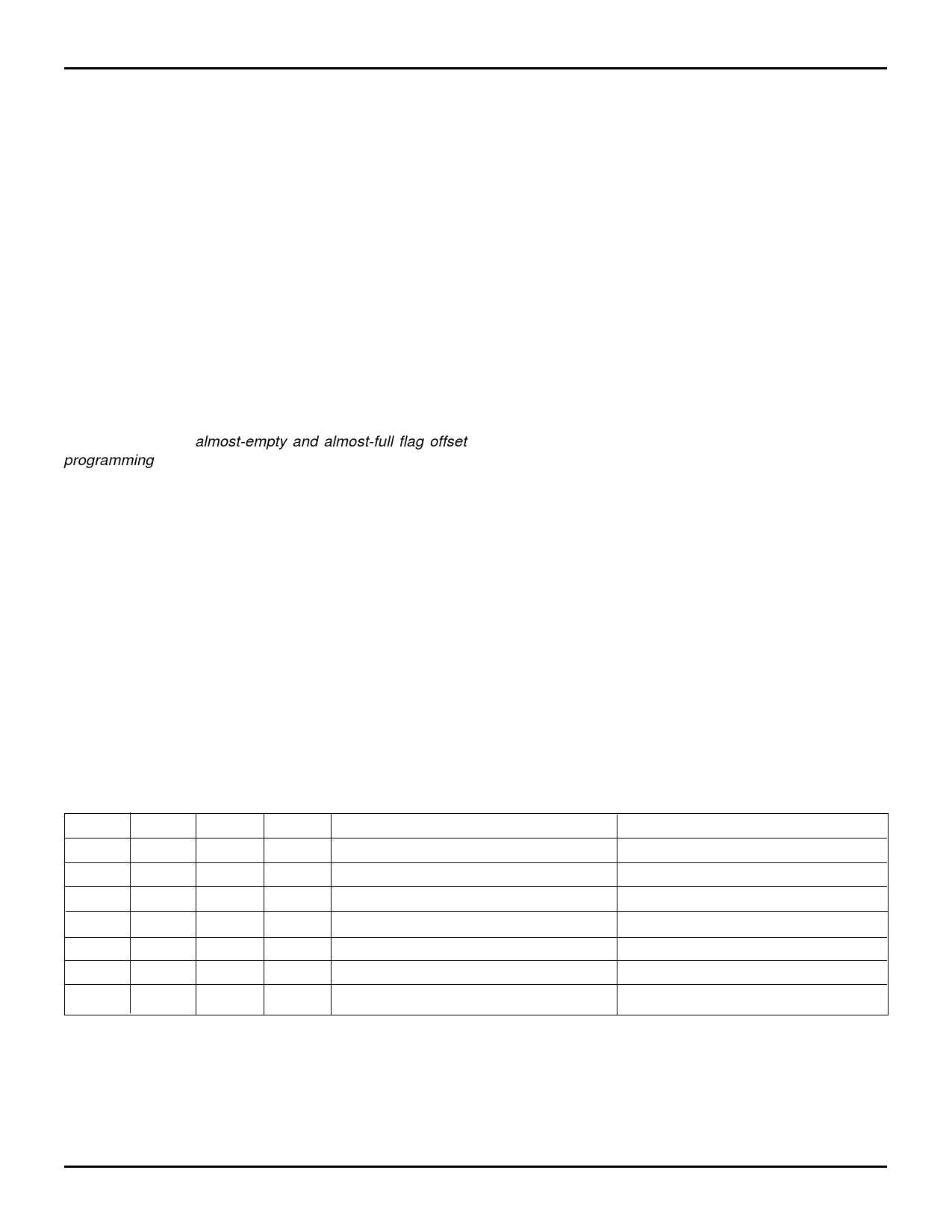

FS1 FS0 RST1 RST2

H

H

↑

X

H

H

X

↑

H

L

↑

X

H

L

X

↑

L

H

↑

X

L

H

X

↑

L

L

↑

↑

X1 AND Y1 REGlSTERS(1)

64

X

16

X

8

X

Programmed from port A

NOTES:

1. X1 register holds the offset for AEB; Y1 register holds the offset for AFA.

2. X2 register holds the offset tor AEA; Y2 register holds the offset for AFB.

Table 1. Flag Programming

X2 AND Y2 REGlSTERS(2)

X

64

X

16

X

8

Programmed from port A

5.22

10