IDT71256SA25 Просмотр технического описания (PDF) - Integrated Device Technology

Номер в каталоге

Компоненты Описание

Список матч

IDT71256SA25 Datasheet PDF : 7 Pages

| |||

IDT71256SA

CMOS STATIC RAM 256K (32K x 8-BIT) IN PE PACKAGES

COMMERCIAL TEMPERATURE RANGE

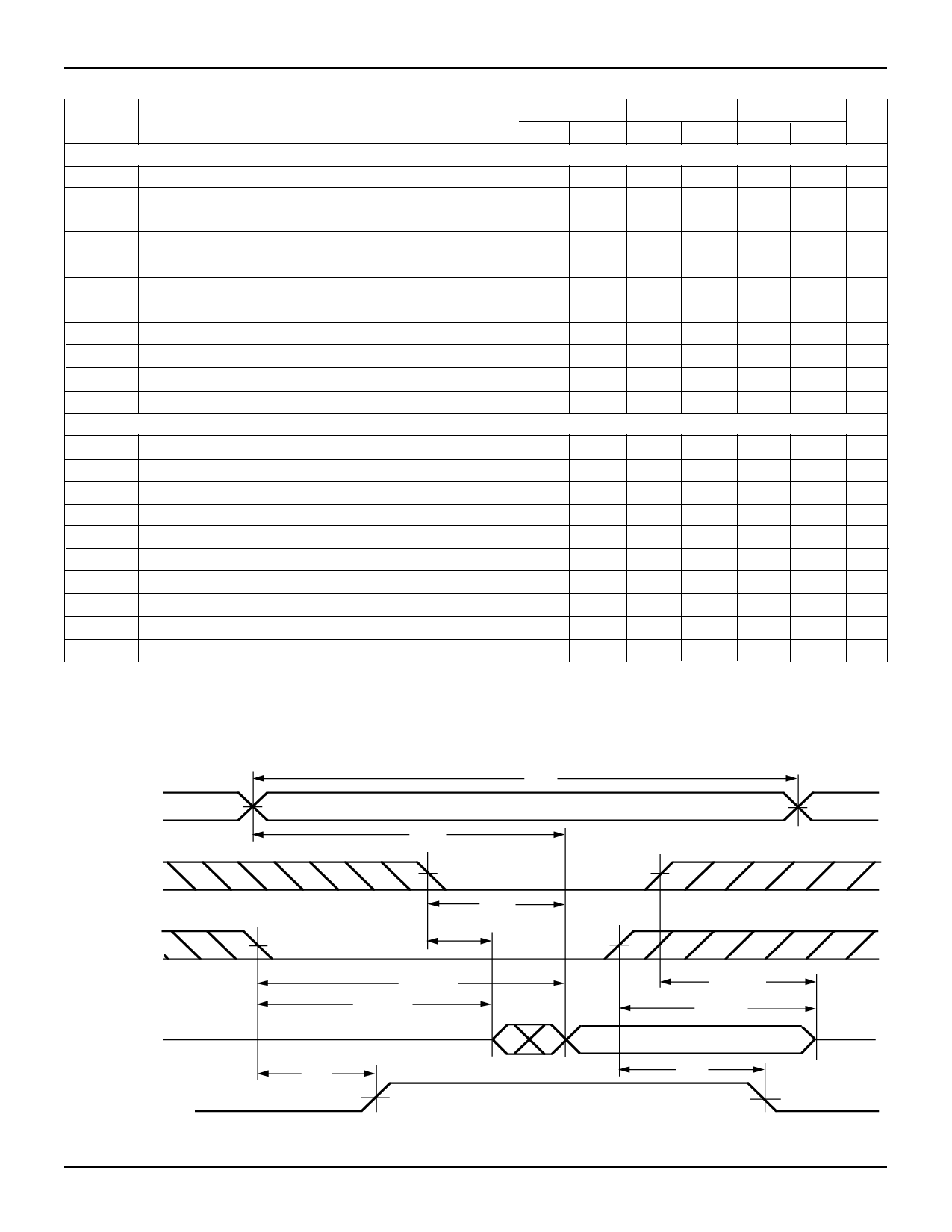

AC ELECTRICAL CHARACTERISTICS (CONTINUED) (VCC = 5.0V ± 10%)

71256SA35

71256SA45

Symbol

Read Cycle

tRC

Read Cycle Time

Parameter

Min. Max. Min. Max.

35

—

45

—

tAA

Address Access Time

—

35

—

45

tACS

tCLZ(1)

tCHZ(1)

Chip Select Access Time

Chip Select to Output in Low-Z

Chip Deselect to Output in High-Z

—

35

—

45

4

—

4

—

0

11

0

11

tOE

tOLZ(1)

tOHZ(1)

Output Enable to Output Valid

Output Enable to Output in Low-Z

Output Disable to Output in High-Z

—

11

—

11

0

—

0

—

0

10

0

10

tOH

tPU(1)

tPD(1)

Output Hold from Address Change

Chip Select to Power Up Time

Chip Deselect to Power Down Time

3

—

3

—

0

—

0

—

—

25

—

25

Write Cycle

tWC

Write Cycle Time

35

—

45

—

tAW

Address Valid to End of Write

20

—

20

—

tCW

Chip Select to End of Write

20

—

20

—

tAS

Address Set-up Time

0

—

0

—

tWP

Write Pulse Width

20

—

20

—

tWR

Write Recovery Time

0

—

0

—

tDW

Data Valid to End of Write

13

—

13

—

tDH

tOW(1)

tWHZ(1)

Data Hold Time

Output Active from End of Write

Write Enable to Output in High-Z

0

—

0

—

4

—

4

—

0

11

0

11

NOTE:

1. This parameter is guaranteed with the AC Load (Figure 2) by device characterization, but is not production tested.

71256SA70

Min. Max. Unit

70

— ns

—

70 ns

—

70 ns

4

— ns

0

11 ns

—

11 ns

0

— ns

0

10 ns

3

— ns

0

— ns

—

25 ns

70

— ns

20

— ns

20

— ns

0

— ns

20

— ns

0

— ns

13

— ns

0

— ns

4

— ns

0

11 ns

3605 tbl 08

TIMING WAVEFORM OF READ CYCLE NO. 1(1)

ADDRESS

tRC

tAA

OE

CS

DATAOUT

VCC SUPPLY ICC

CURRENT

ISB

tOE

tOLZ (5)

tACS (3)

tCLZ (5)

HIGH IMPEDANCE

tPU

tOHZ (5)

tCHZ (5)

DATA OUT VALID

tPD

3605 drw 05

5