IDT7202LA20XEB Просмотр технического описания (PDF) - Integrated Device Technology

Номер в каталоге

Компоненты Описание

Список матч

IDT7202LA20XEB Datasheet PDF : 14 Pages

| |||

CMOS ASYNCHRONOUS FIFO

256 x 9, 512 x 9 and 1,024 x 9

IDT7200L

IDT7201LA

IDT7202LA

FEATURES:

• First-In/First-Out dual-port memory

• 256 x 9 organization (IDT7200)

• 512 x 9 organization (IDT7201)

• 1,024 x 9 organization (IDT7202)

• Low power consumption

— Active: 440mW (max.)

—Power-down: 28mW (max.)

• Ultra high speed—12ns access time

• Asynchronous and simultaneous read and write

• Fully expandable by both word depth and/or bit width

• Pin and functionally compatible with 720X family

• Status Flags: Empty, Half-Full, Full

• Auto-retransmit capability

• High-performance CEMOS™ technology

• Military product compliant to MIL-STD-883, Class B

• Standard Military Drawing #5962-87531, 5962-89666, 5962-89863

and 5962-89536 are listed on this function

• Dual versions available in the TSSOP package. For more informa-

tion, see IDT7280/7281/7282 data sheet

IDT7280 = 2 x IDT7200

IDT7281 = 2 x IDT7201

IDT7282 = 2 x IDT7202

• Industrial temperature range (–40oC to +85oC) is available

(plastic packages only)

DESCRIPTION:

The IDT7200/7201/7202 are dual-port memories that load and empty data

on a first-in/first-out basis. The devices use Full and Empty flags to prevent data

overflow and underflow and expansion logic to allow for unlimited expansion

capability in both word size and depth.

The reads and writes are internally sequential through the use of ring

pointers, with no address information required to load and unload data. Data

is toggled in and out of the devices through the use of the Write (W) and Read

(R) pins.

The devices utilize a 9-bit wide data array to allow for control and parity bits

at the user’s option. This feature is especially useful in data communications

applications where it is necessary to use a parity bit for transmission/reception

error checking. It also features a Retransmit (RT) capability that allows for reset

of the read pointer to its initial position when RT is pulsed LOW to allow for

retransmission from the beginning of data. A Half-Full Flag is available in the

single device mode and width expansion modes.

These FIFOs are fabricated using IDT’s high-speed CMOS technology.

They are designed for those applications requiring asynchronous and

simultaneous read/writes in multiprocessing and rate buffer applications.

Military grade product is manufactured in compliance with the latest revision of

MIL-STD-883, Class B.

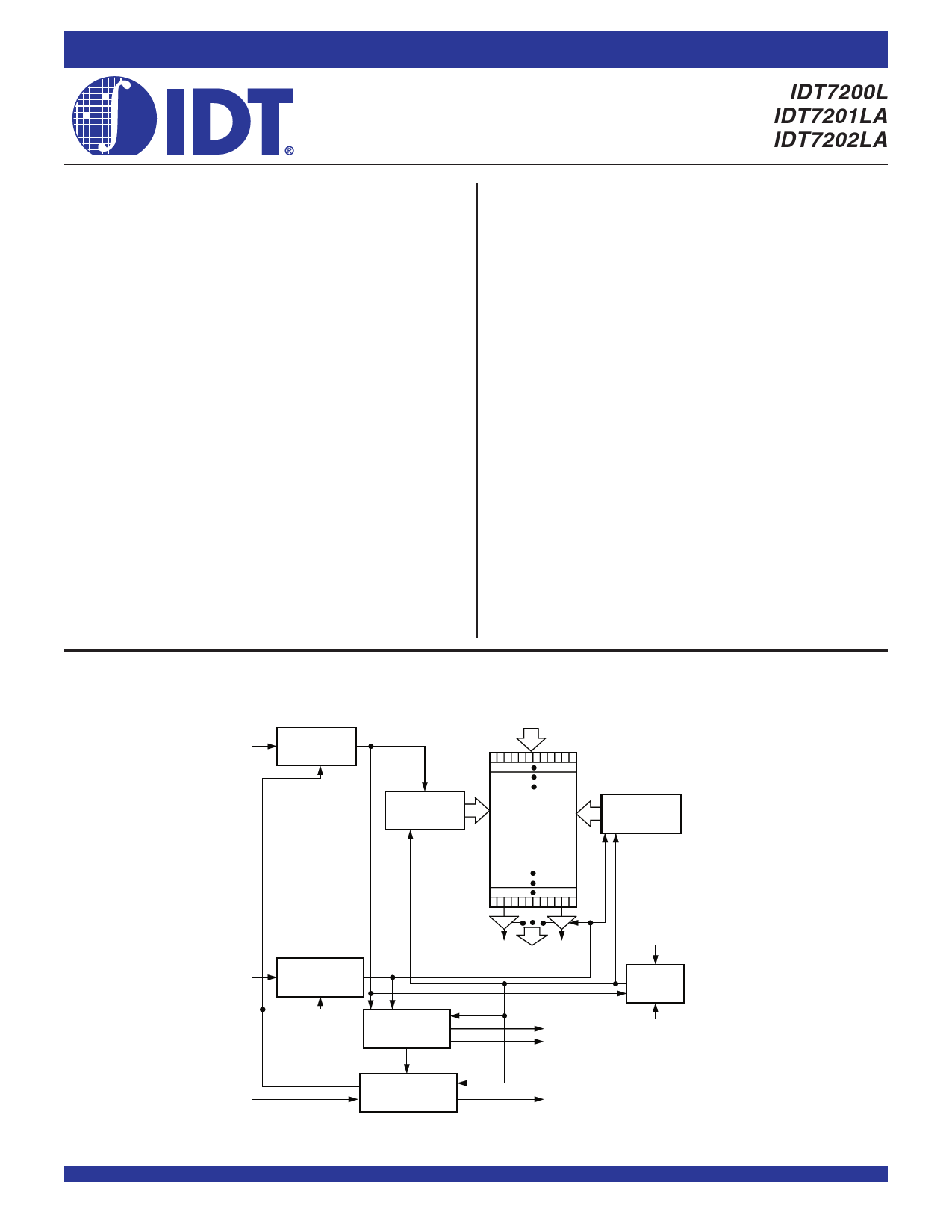

FUNCTIONAL BLOCK DIAGRAM

W

WRITE

CONTROL

DATA INPUTS

(D0-D8)

WRITE

POINTER

RAM

ARRAY

256 x 9

512 x 9

1,024 x 9

READ

POINTER

R

READ

CONTROL

THREE-

STATE

BUFFERS

DATA OUTPUTS

(Q0-Q8)

FLAG

LOGIC

EF

FF

RS

RESET

LOGIC

FL/RT

EXPANSION

XI

LOGIC

XO/HF

2679 drw 01

IDT and the IDT logo are registered trademarks of Integrated Device Technology, Inc.

COMMERCIAL, INDUSTRIAL AND MILITARY TEMPERATURE RANGES

1

2002 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice.

SEPTEMBER 2002

DSC-2679/9