IDT723612L15PQFG Просмотр технического описания (PDF) - Integrated Device Technology

Номер в каталоге

Компоненты Описание

Список матч

IDT723612L15PQFG Datasheet PDF : 25 Pages

| |||

IDT723612

CMOS SYNCBiFIFOTM 64 x 36 x 2

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

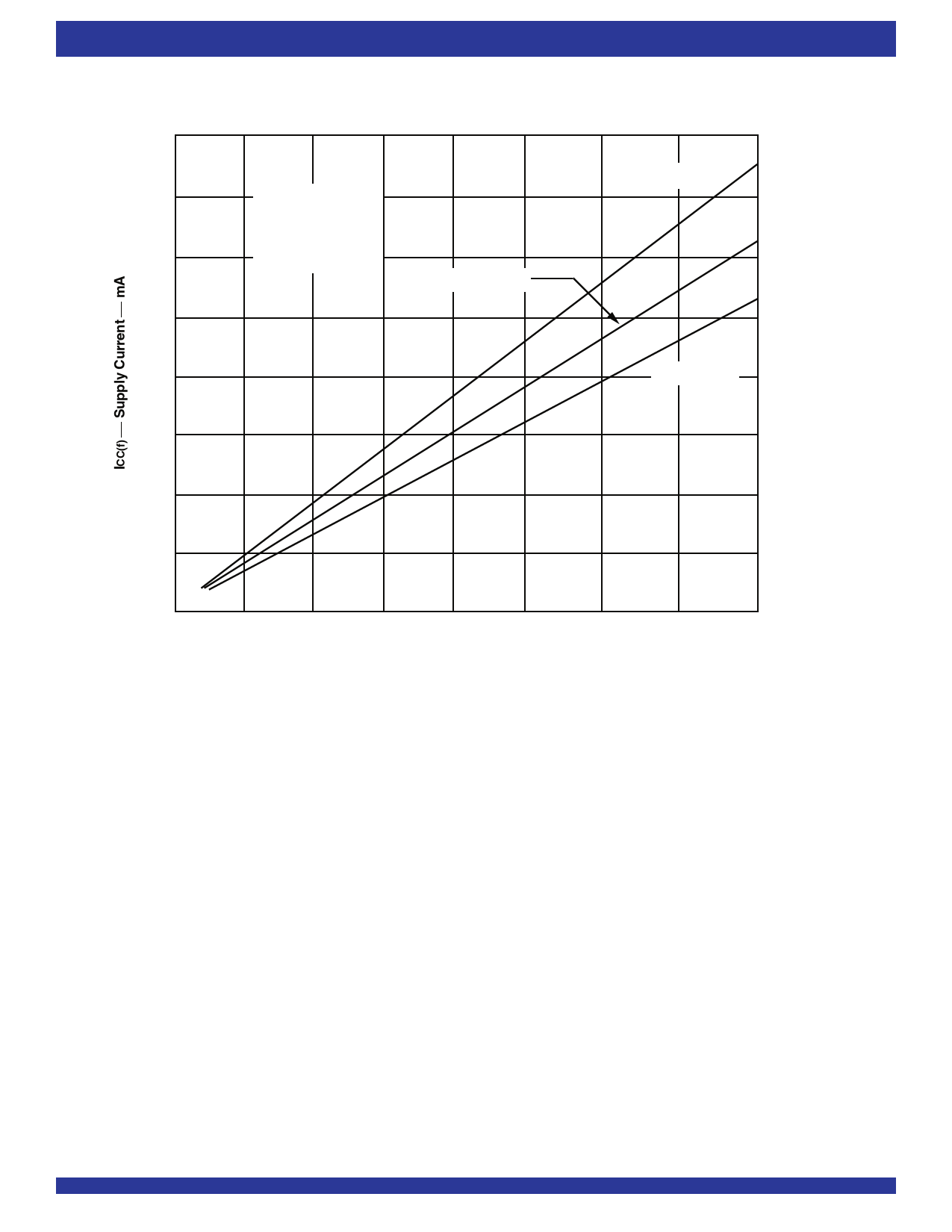

400

350

300

250

200

150

100

50

0

0

fdata = 1/2 fS

TA= 25°C

CL = 0 pF

VCC = 5.0V

VCC = 5.5V

VCC = 4.5V

10

20

30

40

50

60

70

80

fS ⎯ Clock Frequency ⎯ MHz

3136 drw04

Figure 1. Typical Characteristics: Supply Current vs Clock Frequency

CALCULATING POWER DISSIPATION

The ICC(f) current for the graph in Figure 1 was taken while simultaneously reading and writing the FIFO on the IDT723612 with CLKA and CLKB set

to fS. All data inputs and data outputs change state during each clock cycle to consume the highest supply current. Data outputs were disconnected to normalize

the graph to a zero-capacitance load. Once the capacitance load per data-output channel is known, the power dissipation can be calculated with the equation

below.

With ICC(f) taken from Figure 1, the maximum power dissipation (PD) of the IDT723612 may be calculated by:

PD = VCC x ICC(f) + Σ (CL x VCC x (VOH - VOL) x fo)

where:

CL = outputcapacitanceload

fo = switching frequency of an output

VOH = output HIGH level voltage

VOL = output LOW level voltage

When no reads or writes are occurring on the IDT723612, the power dissipated by a single clock (CLKA or CLKB) input running at frequency fS is

calculated by:

PT = VCC x fS x 0.290 mA/MHz

7

FEBRUARY 13, 2009