CS8414-CS Просмотр технического описания (PDF) - Cirrus Logic

Номер в каталоге

Компоненты Описание

Список матч

CS8414-CS Datasheet PDF : 38 Pages

| |||

CS8413 CS8414

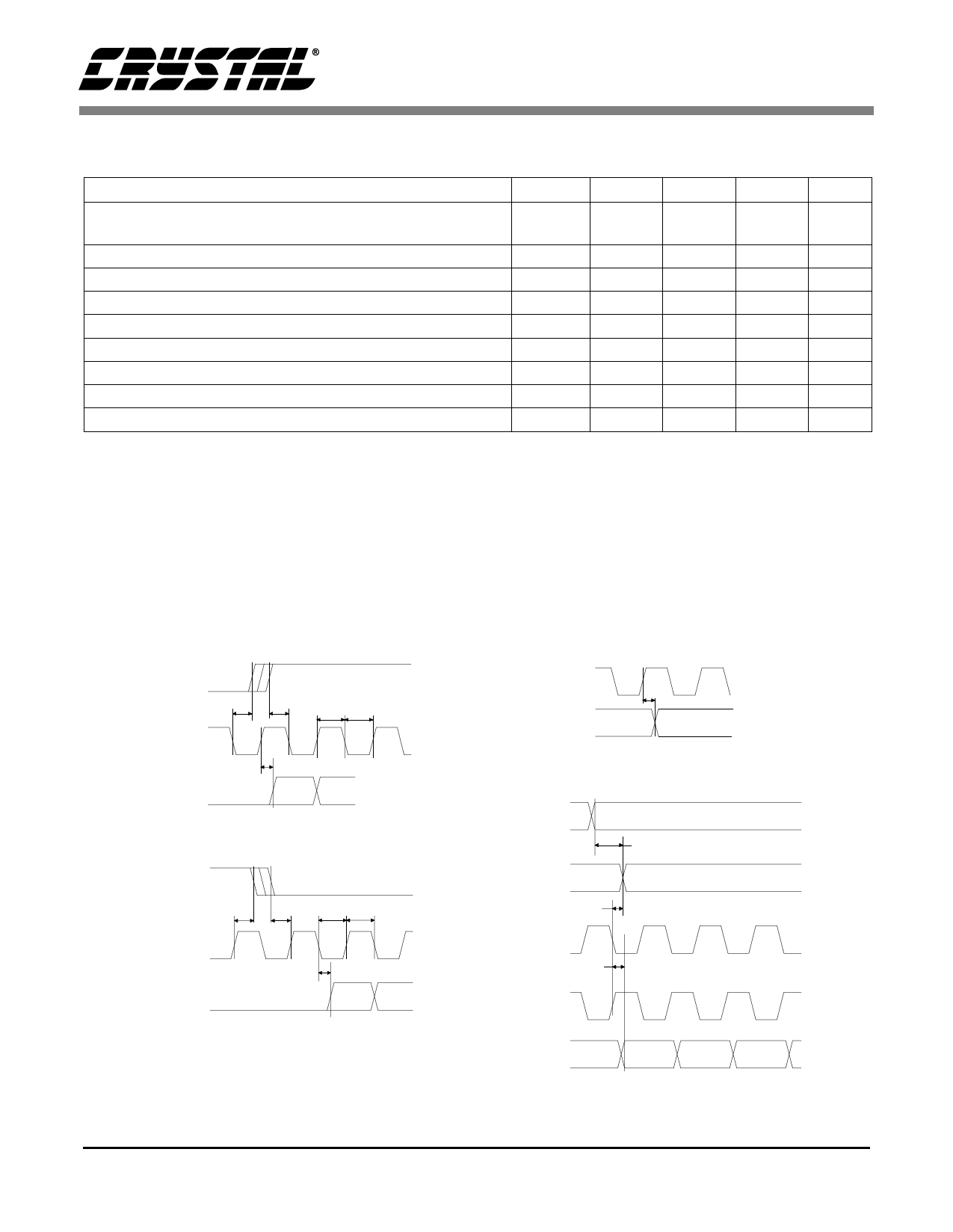

SWITCHING CHARACTERISTICS - SERIAL PORTS

(TA = 25 °C; VD+, VA+ = 5V ± 5%; Inputs: Logic 0 = DGND, Logic 1 = VD+; CL = 20 pF)

Parameters

Symbol Min

Typ

Max

SCK Frequency

Master Mode (Notes 6 and 7)

Slave Mode

(Note 7)

SCK falling to FSYNC delay Master Mode (Notes 7 and 8)

SCK Pulse Width Low

Slave Mode (Note 7)

SCK Pulse Width High

Slave Mode (Note 7)

SCK rising to FSYNC edge delay Slave Mode (Notes 7 and 8)

FSYNC edge to SCK rising setup Slave Mode (Notes 7 and 8)

SCK falling (rising) to SDATA valid

(Note 8)

C, U, CBL valid to FSYNC edge CS8414

(Note 8)

MCK to FSYNC edge delay

FSYNC from RXN/RXP

fsck

tsfdm

tsckl

tsckh

tsfds

tfss

tssv

tcuvf

tmfd

- OWRx32 -

OWRx32

-

128 x FS

-20

-

20

40

-

-

40

-

-

20

-

-

20

-

-

-

-

20

-

1/fsck

-

-

15

-

Units

Hz

Hz

ns

ns

ns

ns

ns

ns

s

ns

Notes: 6. The output word rate, OWR, refers to the frequency at which an audio sample is output from the part.

(A stereo pair is two audio samples.) Therefore, in Master mode, there are always 32 SCK periods in

one audio sample. In Slave mode, exactly 32 SCK periods per audio sample must be provided in most

serial port formats. Therefor, if SCK is 128 x Fs, then SCK must be gated to provide exactly 32 periods

per audio sample.

7. In Master mode, SCK and FSYNC are outputs. In Slave mode, they are inputs. In the CS8413, control

reg. 2 bit 1, MSTR, selects master. In the CS8414, formats 1, 3 and 9 are slaves.

8. The table above assumes data is output on the falling edge and latched on the rising edge. With the

CS8413 the edge is selectable. The table is defined for the CS8413 with control reg. 2 bit 0, SCED, set

to one, and for the CS8414 in formats 2, 3, 5, 6 and 7. For the other formats, the table and figure edges

must be reversed (i.e. “rising” to “falling” and vice versa.)

FSYNC

tsfds

SCK

SDATA

tfss

tsckl tsckh

tssv

MSB

(Mode 1)

FSYNC

tsfds

tfss tsckl tsckh

SCK

SDATA

tssv

MSB

(Mode 3)

Serial Output Timing - Slave Mode

MCK

tmfd

FSYNC

FSYNC Generated From

Received Data

C, U

tcuvf

FSYNC

tsfdm

SCK

(Modes 2,3,5,6, tssv

7,10,12, and 13)

SCK

(Modes 0,1,4,

8,9, and 11)

SDATA

DS240F1

Serial Output Timing -

Master Mode & C, U Port

5