RTL8308B Просмотр технического описания (PDF) - Realtek Semiconductor

Номер в каталоге

Компоненты Описание

Список матч

RTL8308B

RTL8308B Datasheet PDF : 28 Pages

| |||

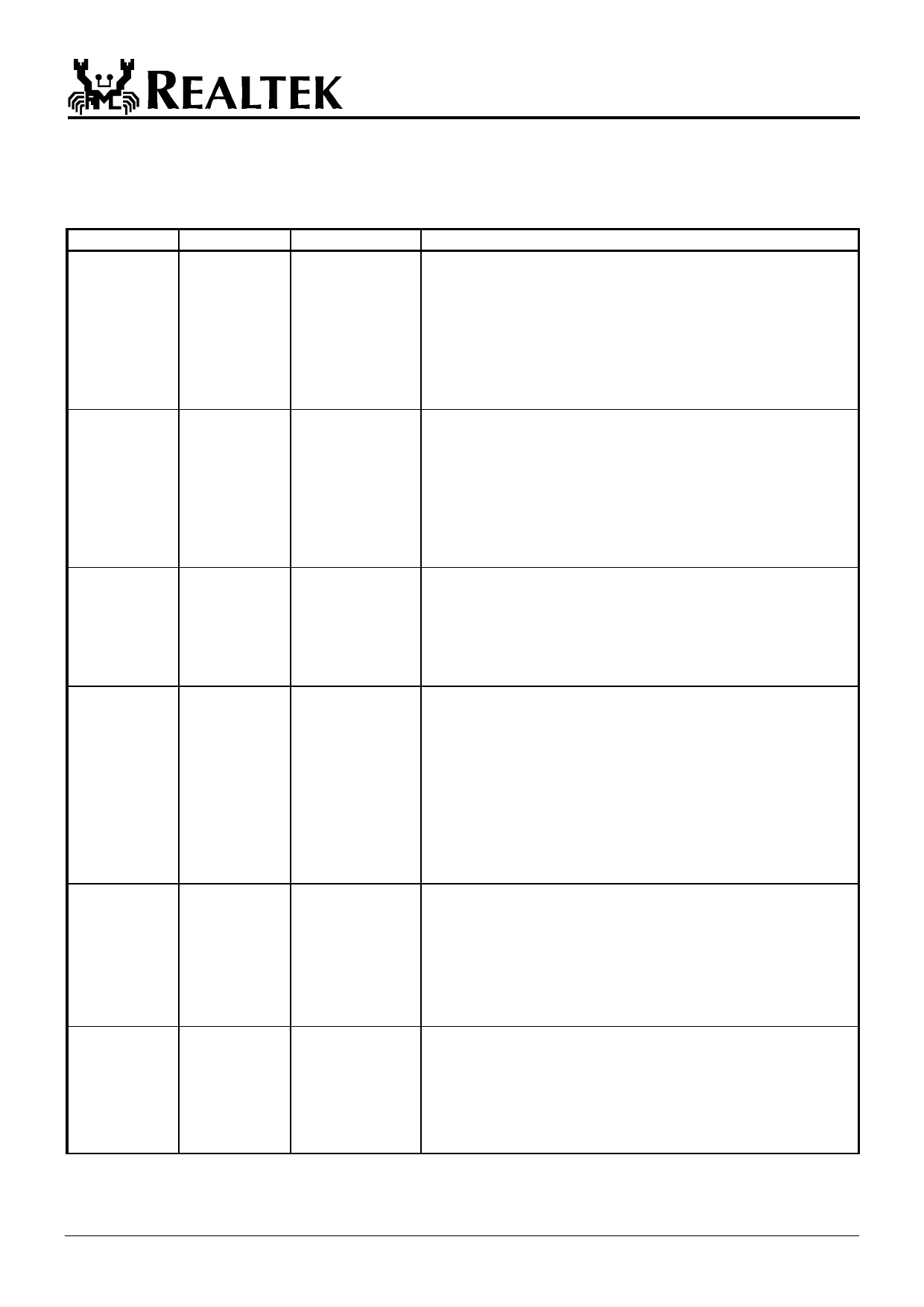

5. Pin Description

RTL8308B

5.1 RMII Interface

Symbol

TXEN[A:H]

Type

O

TXD[0:1][A],

O

TXD[0:1][B],

TXD[0:1][C],

TXD[0:1][D],

TXD[0:1][E],

TXD[0:1][F],

TXD[0:1][G],

TXD[0:1][H]

CRSDV[A:H]

I

RXD[0:1][A],

I

RXD[0:1][B],

RXD[0:1][C],

RXD[0:1][D],

RXD[0:1][E],

RXD[0:1][F],

RXD[0:1][G],

RXD[0:1][H]

REFCLK

I

MDC

O

Pin No

7,13,24,58,

68,76,86,92

8,9,14,15,26,

27,59,60,69,

70,77,78,87,88,

93,94

Description

Transmit Enable: The RTL8308B asserts high to indicate

that valid di-bit data for transmission is presented on

TXD[1:0], and transitions synchronously with respect to

REFCLK.. TXEN will be asserted synchronously with the first

nibble of the preamble and will remain asserted while all

di-bits that are to be transmitted are presented. TXEN will be

negated prior to the first REFCLK rising edge following the

final di-bit of a frame.

Transmit Data [1:0]: TXD[1:0] will transition synchronously

with respect to REFCLK. When TXEN is asserted, TXD[1:0]

is accepted for transmission by the PHY. TXD[1:0] will be

‘00’ to indicate idle when TXEN is deasserted.

10,18,28,61,

72,79,89,96

11,12,19,20,

29,31,62,63,

73,74,80,81,

90,91,97,98

47

43

CRSDV Signals: This signal will be asserted high by the

PHY when the medium is active. It is asserted asynchronously

on detection of carrier due to criteria defined in the IEEE

802.3 specifications. Loss of carrier will result in the

deassertion of this pin, synchronous to the cycle of the

reference clock, REFCLK.

Receive Data [1:0]: The RTL8308B captures the receive data

on the rising edge of REFCLK when CRSDV is asserted high.

When CRSDV is asserted high, RXD[1:0] will transition

synchronously to REFCLK. For each clock period in which

CRSDV is asserted, RXD[1:0] transfers two bits of recovered

data from the PHY. Values other than ‘00’ on RXD[1:0] while

RXDV as recovered from CRSDV is deasserted will be

ignored by the controller. Upon assertion of CRSDV, the PHY

will ensure that RXD[1:0] = ‘00’ until proper receive

decoding takes place.

RMII Reference Clock Input: A continuous clock which

provides the timing reference for CRS_DV, RXD[1:0],

TX_EN, and TXD[1:0]. It is a 50 MHz OSC, 3.3V, +/-50ppm,

0˚ C ~70˚ C, symmetry 45%~55%, Rise/Fall time 5ns, supply

40mA.

It is assumed that the PHY uses REFCLK as the network clock so no

buffering is required on the transmit data path.

Management Data Clock: A clock source common to all

ports, generated by the controller with a frequency of 312.5

kHz, it is used to synchronize the MII data stream (MDIO) for

transferring MII management data between the controller and

transceivers.

This pin is Tri-state at reset.

2002/01/23

6

Rev. 2.0