RTC-8563SA Просмотр технического описания (PDF) - Epson ToYoCom

Номер в каталоге

Компоненты Описание

Список матч

RTC-8563SA Datasheet PDF : 2 Pages

| |||

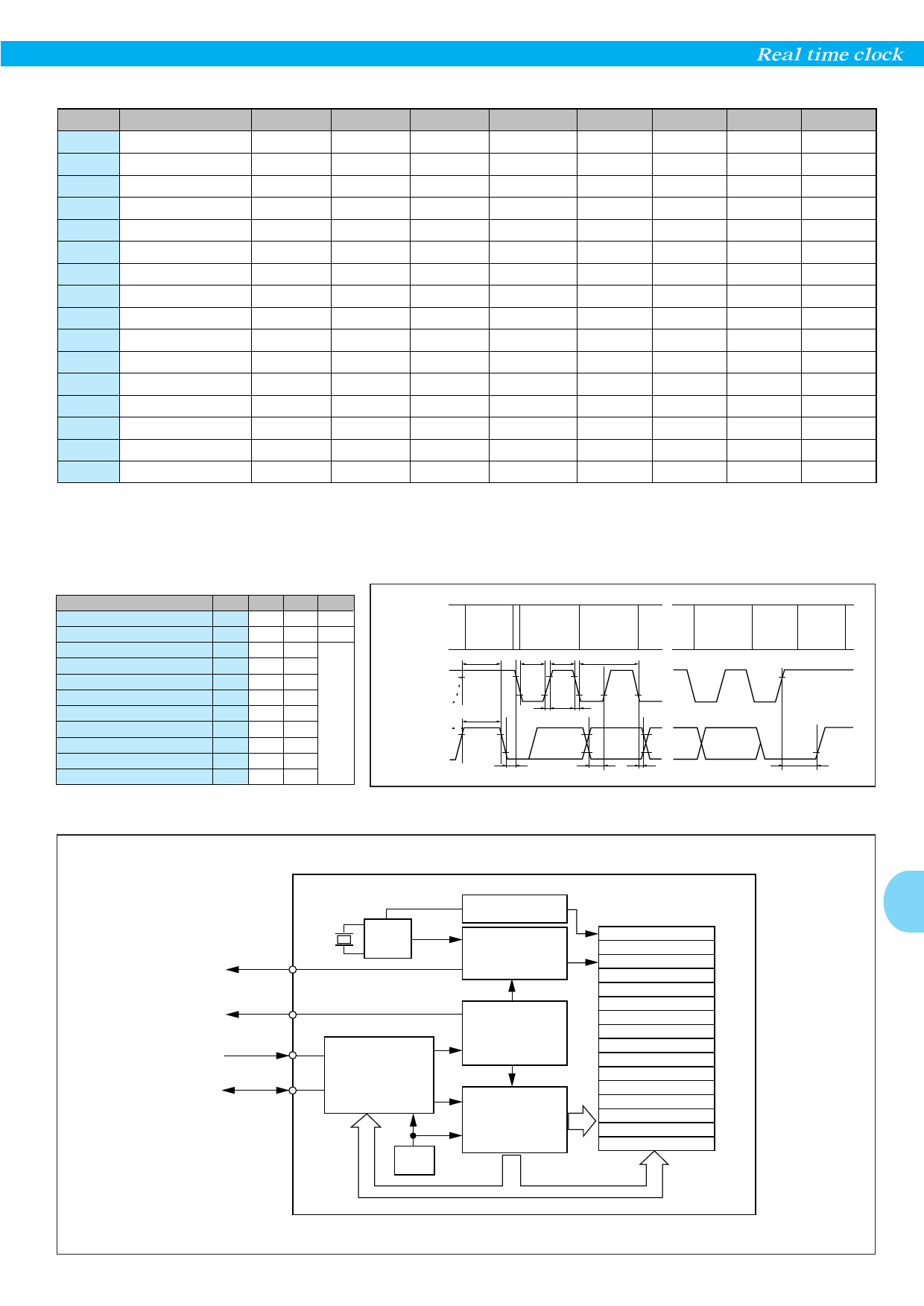

■レジスタテーブル

アドレス

レジスタ名

bit 7

00

Control1

TEST

01

Control2

0

02

Seconds

VL

03

Minutes

※

04

Hours

※

05

Days

※

06

Weekdays

※

07

Months / Century

C

08

Years

Year80

09

Minutes Alarm

AE

0A

Hour Alarm

AE

0B

Day Alarm

AE

0C

Weekday Alarm

AE

0D

CLKOUT frequency

FE

0E

Timer control

TE

0F

Timer

128

0: ゼロを設定してください。

bit 6

0

0

S40

Min40

※

※

※

※

Year40

A-Min40

A-Hr40

※

※

※

※

64

bit 5

STOP

0

S20

Min20

Hour20

Day20

※

※

Year20

A-Min20

A-Hr20

A-Day20

※

※

※

32

bit 4

0

TI / TP

S10

Min10

Hour10

Day10

※

Month10

Year10

A-Min10

A-Hr10

A-Day10

※

※

※

16

bit 3

TEST

AF

S8

Min8

Hour8

Day8

※

Month8

Year8

A-Min8

A-Hr8

A-Day8

※

※

※

8

bit 2

0

TF

S4

Min4

Hour4

Day4

W4

Month4

Year4

A-Min4

A-Hr4

A-Day4

A-W4

※

※

4

Real time clock

bit 1

0

AIE

S2

Min2

Hour2

Day2

W2

Month2

Year2

A-Min2

A-Hr2

A-Day2

A-W2

FD1

TD1

2

bit 0

0

TIE

S1

Min1

Hour1

Day1

W1

Month1

Year1

A-Min1

A-Hr1

A-Day1

A-W1

FD0

TD0

1

■スイッチング特性

■タイミングチャート

特記無き場合、(VDD= 0V, Ta= ー40℃〜+85℃)

項 目

記 号 Min. Max. 単 位

SCLクロック周波数

fSCL

バス上の許容スパイク時間

tSW

400 kHz

50 ns

Protocol

START

CONDITION

(S)

BIT 7

MSB

(A7)

BIT 0

(A6)

BIT 0

LSB

(R/W)

ASK

(A)

開始条件セットアップ時間

開始条件ホールド時間

tSU,STA 0.6

tHD,STA 0.6

tSU;STA

tLOW tHIGH

1/fSCL

SCL L 時間

SCL H 時間

tLOW 1.3

tHIGH 0.6

SCL

SCL,SDA 立ち上がり時間

tr

0.3 μs

tBUF

tr

tf

SCL,SDA 立ち下がり時間

tf

0.3

データセットアップ時間

tSU;DAT 100

SDA

データホールド時間

停止条件セットアップ時間

tHD;DAT 0

tSU;STO 4.0

tHD;STA

tSU;DAT

tHD;DAT

■回路構成図

STOP

CONDITION

(P)

tSU;STO

CLKOUT

/ INT

SCL

SDA

32.768kHz

CRYSTAL

OSC

I2C-BUS

INTERFACE

POR

Voltage Detector

DIVIDER

CONTROL

LOGIC

ADDRESS

REGISTER

Control 1

00

Control 2

Seconds

Minutes

Hours

Days

Weekdays

Month / Century

Years

Minutes Alarm

Hour Alarm

Day Alarm

Weekday Alarm

CLKOUT frequency

Timer Control

Timer

0F

62