W78E516BP-24 Просмотр технического описания (PDF) - Winbond

Номер в каталоге

Компоненты Описание

Список матч

W78E516BP-24 Datasheet PDF : 26 Pages

| |||

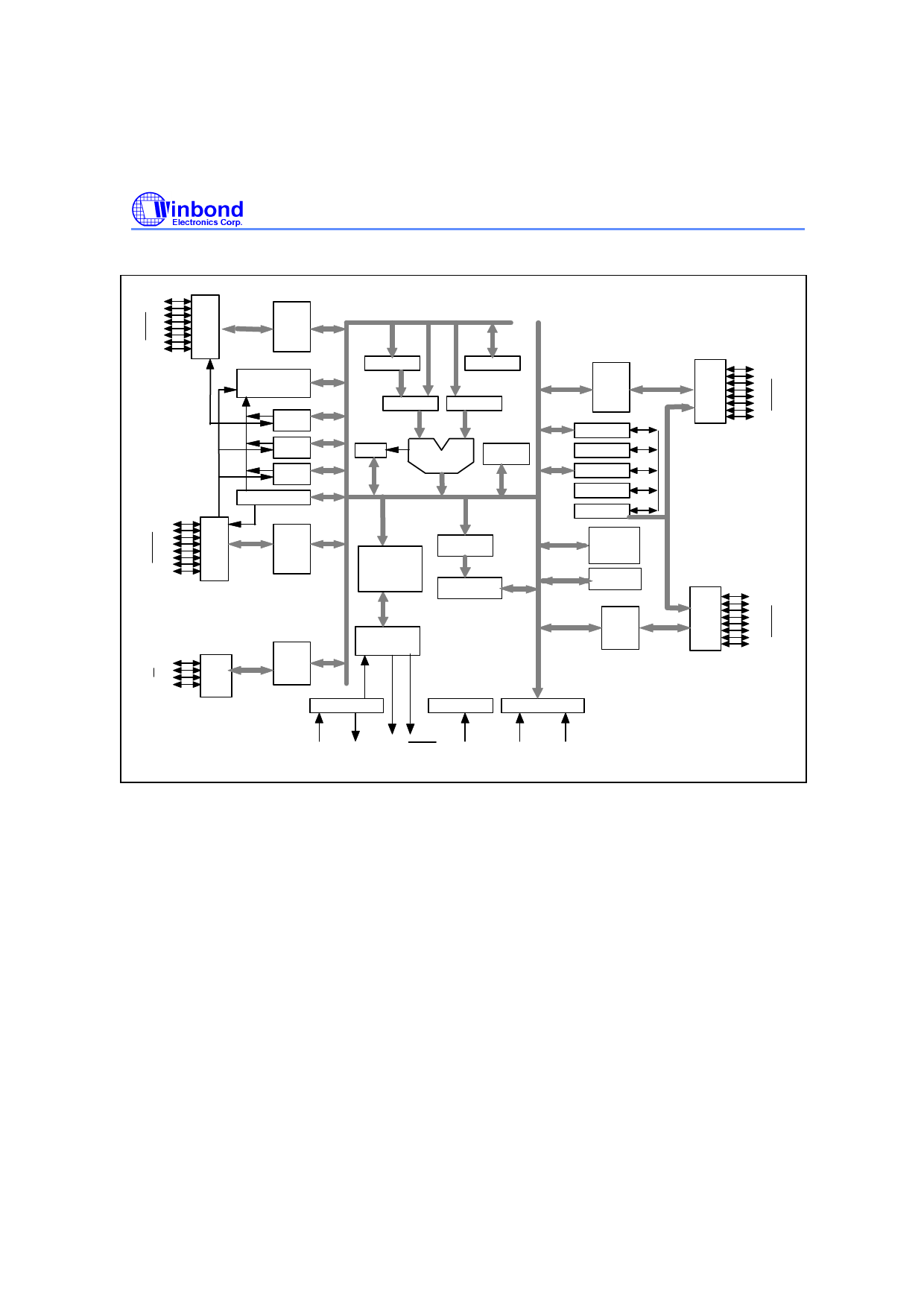

W78E516B

BLOCK DIAGRAM

P1.0

P1.7

P3.0

P3.7

P4.0

P4.3

Port

1

Port

3

Port

4

Port 1

Latch

Interrupt

Timer

2

Timer

0

Timer

1

UART

Port 3

Latch

Port 4

Latch

ACC

T1

B

T2

PSW

ALU

Stack

Pointer

Instruction

Decoder

&

Sequencer

Bus & Clock

Controller

SFR RAM

Address

512 bytes

RAM & SFR

Port 0

Latch

DPTR

Temp Reg.

PC

Incrementor

Addr. Reg.

64KB

MTP-ROM

4KB

MTP-ROM

Port 2

Latch

Oscillator

Reset Block

ALE

XTAL1 XTAL2

PSEN

RST

Power control

VCC

Vss

P0.0

Port

0

P0.7

P2.0

Port

2

P2.7

FUNCTIONAL DESCRIPTION

The W78E516B architecture consists of a core controller surrounded by various registers, four

general purpose I/O ports, one special purpose programmable 4-bits I/O port, 512 bytes of RAM,

three timer/counters, a serial port and an internal 74373 latch and 74244 buffer which can be

switched to port2. The processor supports 111 different opcodes and references both a 64K program

address space and a 64K data storage space.

RAM

The internal data RAM in the W78E516B is 512 bytes. It is divided into two banks: 256 bytes of

scratchpad RAM and 256 bytes of AUX-RAM. These RAMs are addressed by different ways.

• RAM 0H−127H can be addressed directly and indirectly as the same as in 8051. Address pointers

are R0 and R1 of the selected register bank.

• RAM 128H−255H can only be addressed indirectly as the same as in 8051. Address pointers are

R0, R1 of the selected registers bank.

-4-