MCM69P737TQ3.5 Просмотр технического описания (PDF) - Motorola => Freescale

Номер в каталоге

Компоненты Описание

Список матч

MCM69P737TQ3.5 Datasheet PDF : 20 Pages

| |||

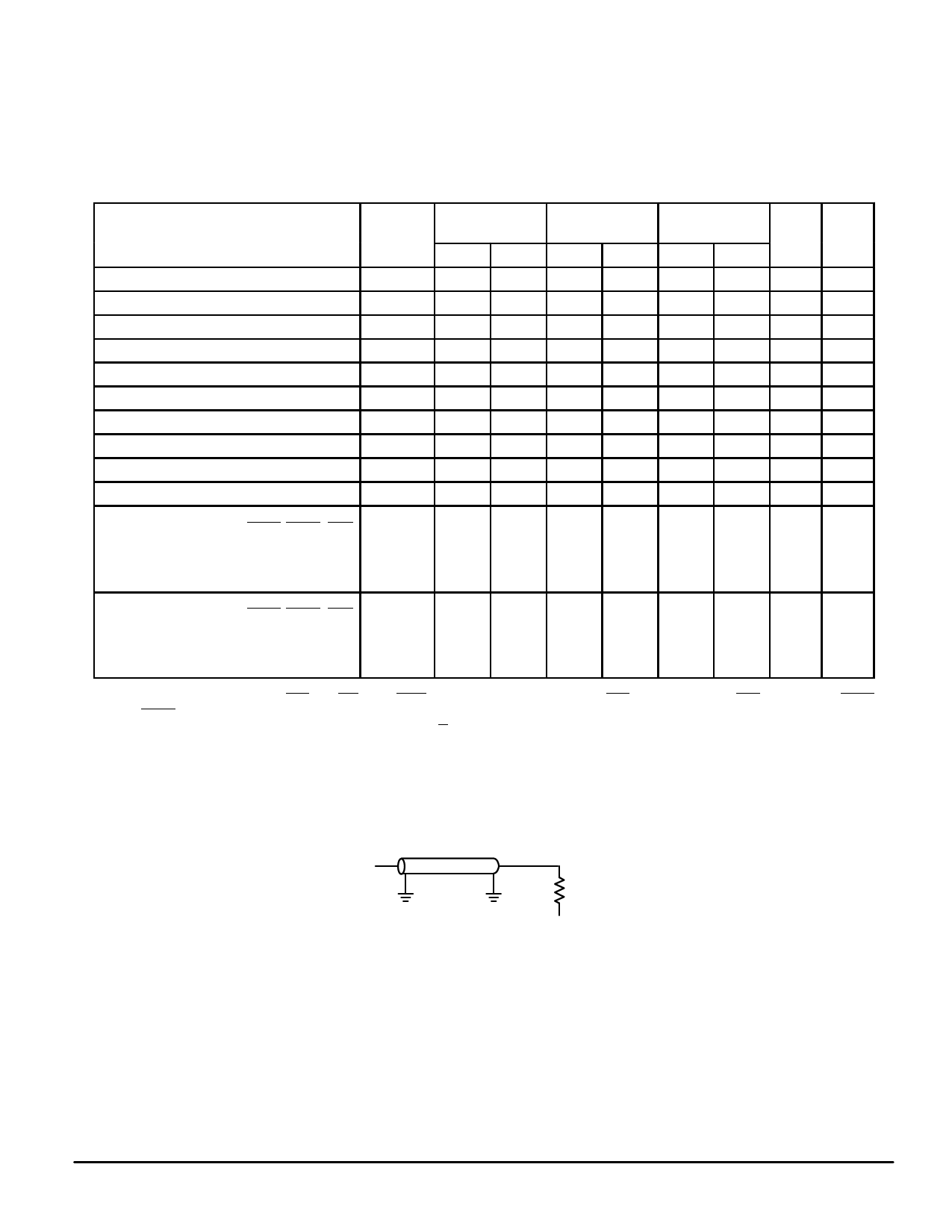

AC OPERATING CONDITIONS AND CHARACTERISTICS

(VDD = 3.3 v + 10%, – 5%, TA = 0 to 70°C, Unless Otherwise Noted)

Input Timing Measurement Reference Level . . . . . . . . . . . . . . 1.25 V

Input Pulse Levels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0 to 2.5 V

Input Rise/Fall Times . . . . . . . . . . . . . . . . . . . . . 1.0 V/ns (20 to 80%)

Output Timing Reference Level . . . . . . . . . . . . . . . . . . . . . . . . . 1.25 V

Output Load . . . . . . . . . . . . . . See Figure 2 Unless Otherwise Noted

READ/WRITE CYCLE TIMING (See Notes 1 and 2)

MCM69P737–3.5 MCM69P737–3.8 MCM69P737–4

166 MHz

150 MHz

133 MHz

Parameter

Symbol

Min

Max

Min

Max

Min

Max Unit Notes

Cycle Time

tKHKH

6

—

6.7

—

7.5

—

ns

Clock High Pulse Width

tKHKL

2.4

—

2.6

—

3

—

ns

3

Clock Low Pulse Width

tKLKH

2.4

—

2.6

—

3

—

ns

3

Clock Access Time

tKHQV

—

3.5

—

3.8

—

4

ns

Output Enable to Output Valid

tGLQV

—

3.5

—

3.5

—

3.8

ns

Clock High to Output Active

tKHQX1

0

—

0

—

0

—

ns

4, 5

Clock High to Output Change

tKHQX2

1.5

—

1.5

—

1.5

—

ns

4

Output Enable to Output Active

tGLQX

0

—

0

—

0

—

ns

4, 5

Output Disable to Q High–Z

tGHQZ

—

3.5

—

3.5

—

3.8

ns

4, 5

Clock High to Q High–Z

tKHQZ

1.5

6

1.5

6.7

1.5

7.5

ns

4, 5

Setup Times:

Address tADKH

1.5

—

1.5

—

1.5

—

ns

ADSP, ADSC, ADV tADSKH

Data In tDVKH

Write tWVKH

Chip Enable tEVKH

Hold Times:

Address tKHAX

0.5

—

0.5

—

0.5

—

ns

ADSP, ADSC, ADV tKHADSX

Data In tKHDX

Write tKHWX

Chip Enable tKHEX

NOTES:

1. Write is defined as either any SBx and SW low or SGW is low. Chip Enable is defined as SE1 low, SE2 high, and SE3 low whenever ADSP

or ADSC is asserted.

2. All read and write cycle timings are referenced from K or G.

3. In order to reduce test correlation issues and to reduce the effects of application specific input edge rate variations on correlation between

data sheet parameters and actual system performance, FSRAM AC parametric specifications are always specified at VDDQ/2. In some

design exercises, it is desirable to evaluate timing using other reference levels. Since the maximum test input edge rate is known and is

given in the AC Test Conditions section of the data sheet as 1 V/ns, one can easily interpolate timing values to other reference levels.

4. This parameter is sampled and not 100% tested.

5. Measured at ± 200 mV from steady state.

OUTPUT

Z0 = 50 Ω

RL = 50 Ω

1.25 V

Figure 2. AC Test Load

MCM69P737

10

MOTOROLA FAST SRAM