MCM63P819KZP150R Просмотр технического описания (PDF) - Motorola => Freescale

Номер в каталоге

Компоненты Описание

Список матч

MCM63P819KZP150R

MCM63P819KZP150R Datasheet PDF : 20 Pages

| |||

Freescale Semiconductor, Inc.

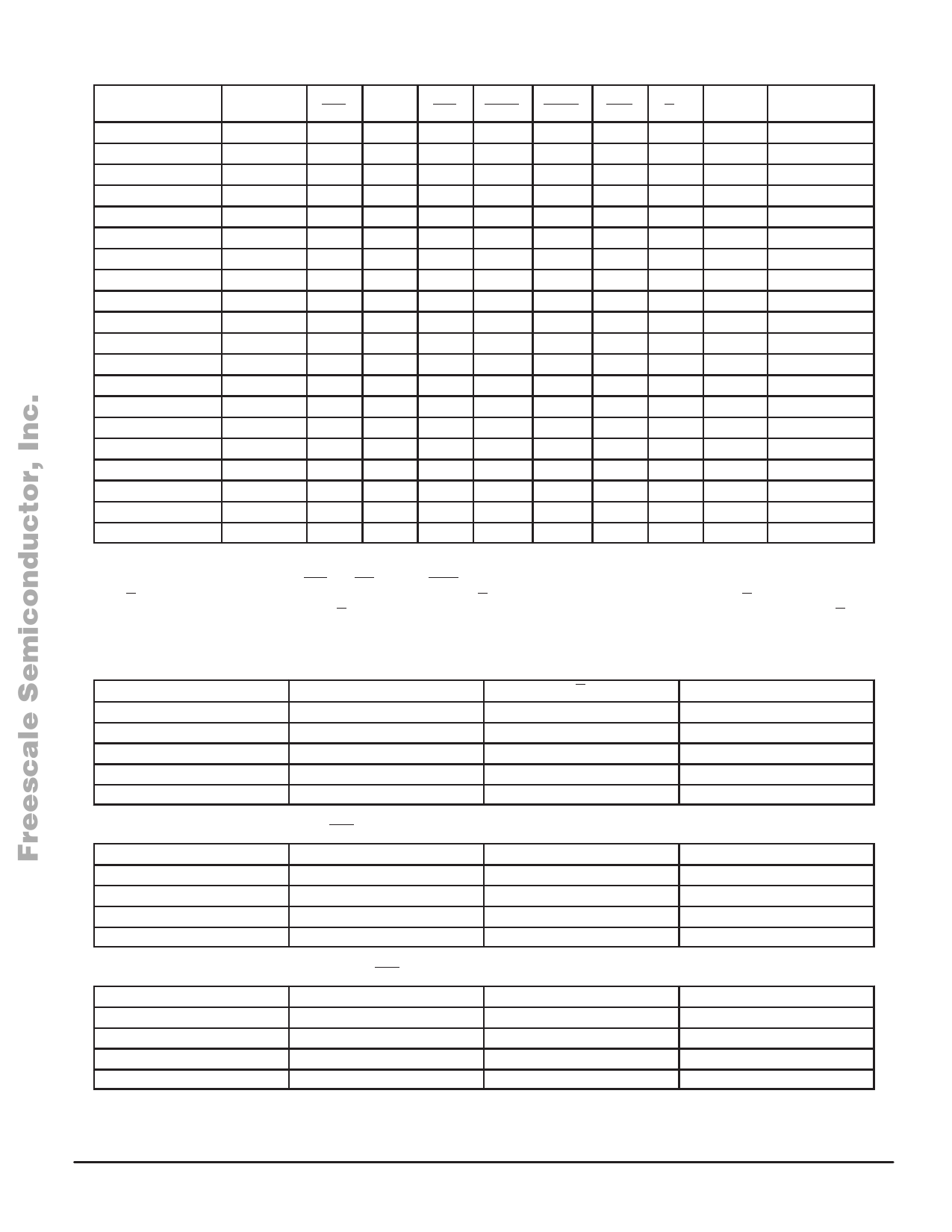

TRUTH TABLE (See Notes 1 Through 5)

Next Cycle

Address

Used

SE1

SE2

SE3 ADSP ADSC ADV

G3

DQx

Write 2, 4

Deselect

None

1

X

X

X

0

X

X

High–Z

X

Deselect

None

0

X

1

0

X

X

X

High–Z

X

Deselect

None

0

0

X

0

X

X

X

High–Z

X

Deselect

None

X

X

1

1

0

X

X

High–Z

X

Deselect

None

X

0

X

1

0

X

X

High–Z

X

Begin Read

External

0

1

0

0

X

X

X

High–Z

X

Begin Read

External

0

1

0

1

0

X

X

High–Z

READ

Continue Read

Next

X

X

X

1

1

0

1

High–Z

READ

Continue Read

Next

X

X

X

1

1

0

0

DQ

READ

Continue Read

Next

1

X

X

X

1

0

1

High–Z

READ

Continue Read

Next

1

X

X

X

1

0

0

DQ

READ

Suspend Read

Current

X

X

X

1

1

1

1

High–Z

READ

Suspend Read

Current

X

X

X

1

1

1

0

DQ

READ

Suspend Read

Current

1

X

X

X

1

1

1

High–Z

READ

Suspend Read

Current

1

X

X

X

1

1

0

DQ

READ

Begin Write

External

0

1

0

1

0

X

X

High–Z

WRITE

Continue Write

Next

X

X

X

1

1

0

X

High–Z

WRITE

Continue Write

Next

1

X

X

X

1

0

X

High–Z

WRITE

Suspend Write

Current

X

X

X

1

1

1

X

High–Z

WRITE

Suspend Write

Current

1

X

X

X

1

1

X

High–Z

WRITE

NOTES:

1. X = don’t care. 1 = logic high. 0 = logic low.

2. Write is defined as either 1) any SBx and SW low or 2) SGW is low.

3. G is an asynchronous signal and is not sampled by the clock K. G drives the bus immediately (tGLQX) following G going low.

4. On write cycles that follow read cycles, G must be negated prior to the start of the write cycle to ensure proper write data setup times. G must

also remain negated at the completion of the write cycle to ensure proper write data hold times.

ASYNCHRONOUS TRUTH TABLE

Operation

ZZ

Read

L

Read

L

Write

L

Deselected

L

Sleep

H

G

I/O Status

L

Data Out (DQx)

H

High–Z

X

High–Z

X

High–Z

X

High–Z

LINEAR BURST ADDRESS TABLE (LBO = VSS)

1st Address (External)

2nd Address (Internal)

X . . . X00

X . . . X01

X . . . X01

X . . . X10

X . . . X10

X . . . X11

X . . . X11

X . . . X00

3rd Address (Internal)

X . . . X10

X . . . X11

X . . . X00

X . . . X01

4th Address (Internal)

X . . . X11

X . . . X00

X . . . X01

X . . . X10

INTERLEAVED BURST ADDRESS TABLE (LBO = VDD)

1st Address (External)

2nd Address (Internal)

X . . . X00

X . . . X01

X . . . X01

X . . . X00

X . . . X10

X . . . X11

X . . . X11

X . . . X10

3rd Address (Internal)

X . . . X10

X . . . X11

X . . . X00

X . . . X01

4th Address (Internal)

X . . . X11

X . . . X10

X . . . X01

X . . . X00

MOTOROLA FAST SRAM

For More Information On This Product, MCM63P737K•MCM63P819K

Go to: www.freescale.com

9