MB88154PNF-G-112-JN-ERE1 Просмотр технического описания (PDF) - Fujitsu

Номер в каталоге

Компоненты Описание

Список матч

MB88154PNF-G-112-JN-ERE1 Datasheet PDF : 18 Pages

| |||

MB88154

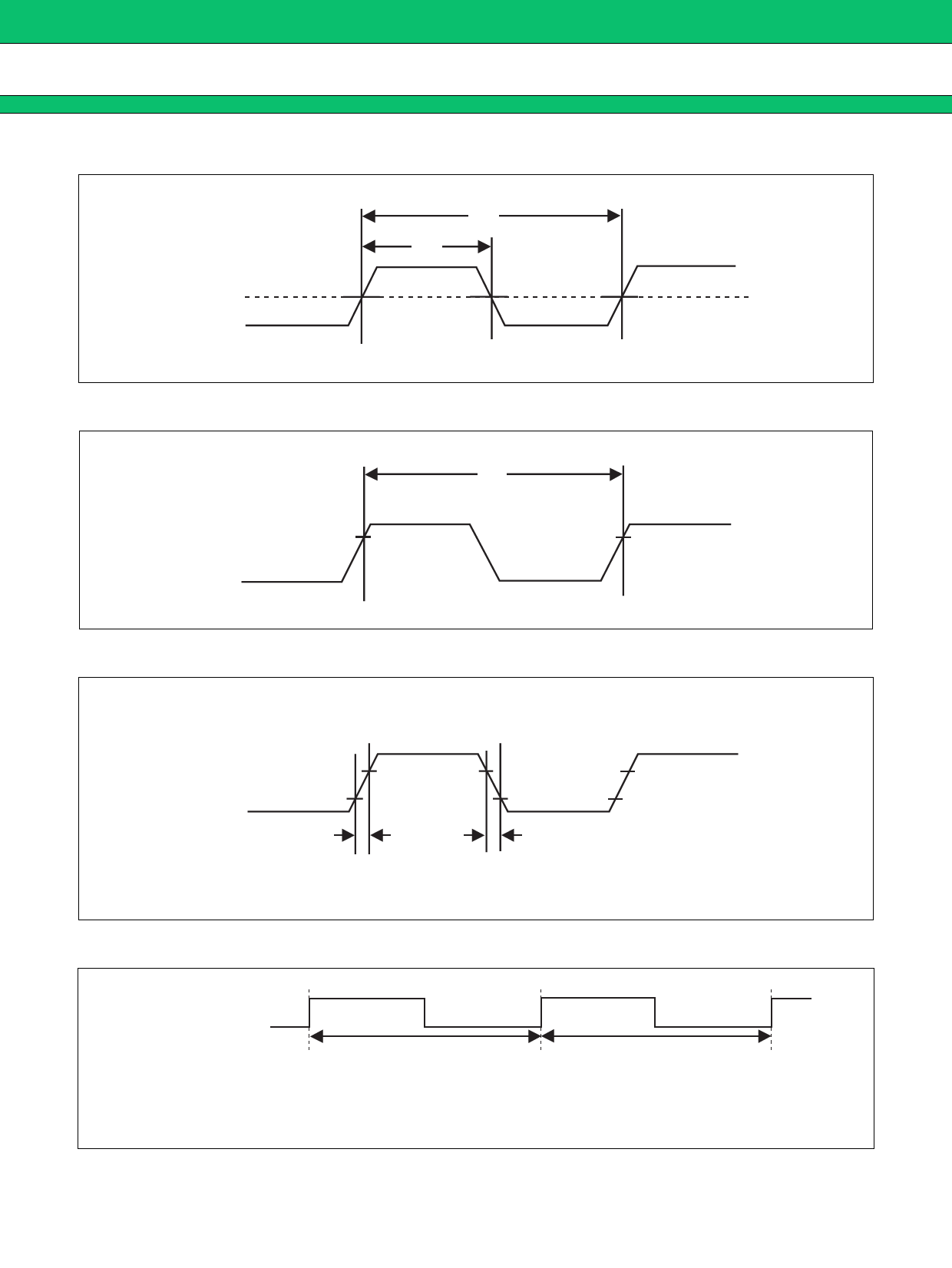

■ OUTPUT CLOCK DUTY CYCLE (tDCC, tDCR = tb/ta)

ta

tb

CKOUT,

REFOUT

■ INPUT FREQUENCY (fin = 1/tin)

tin

XIN

■ OUTPUT SLEW RATE (SR)

1.5 V

0.8 VDD

CKOUT,

REFOUT

tr

Note : SR = (2.4−0.4) /tr, SR = (2.4−0.4) /tf

2.4 V

0.4 V

tf

■ CYCLE-CYCLE JITTER (tJC = | tn − tn + 1 |)

CKOUT

tn

tn+1

Note : Cycle-cycle jitter is defined the difference between a certain cycle and immediately after

(or, immediately before) .

10