MB86613S Просмотр технического описания (PDF) - Fujitsu

Номер в каталоге

Компоненты Описание

Список матч

MB86613S Datasheet PDF : 134 Pages

| |||

Preliminary

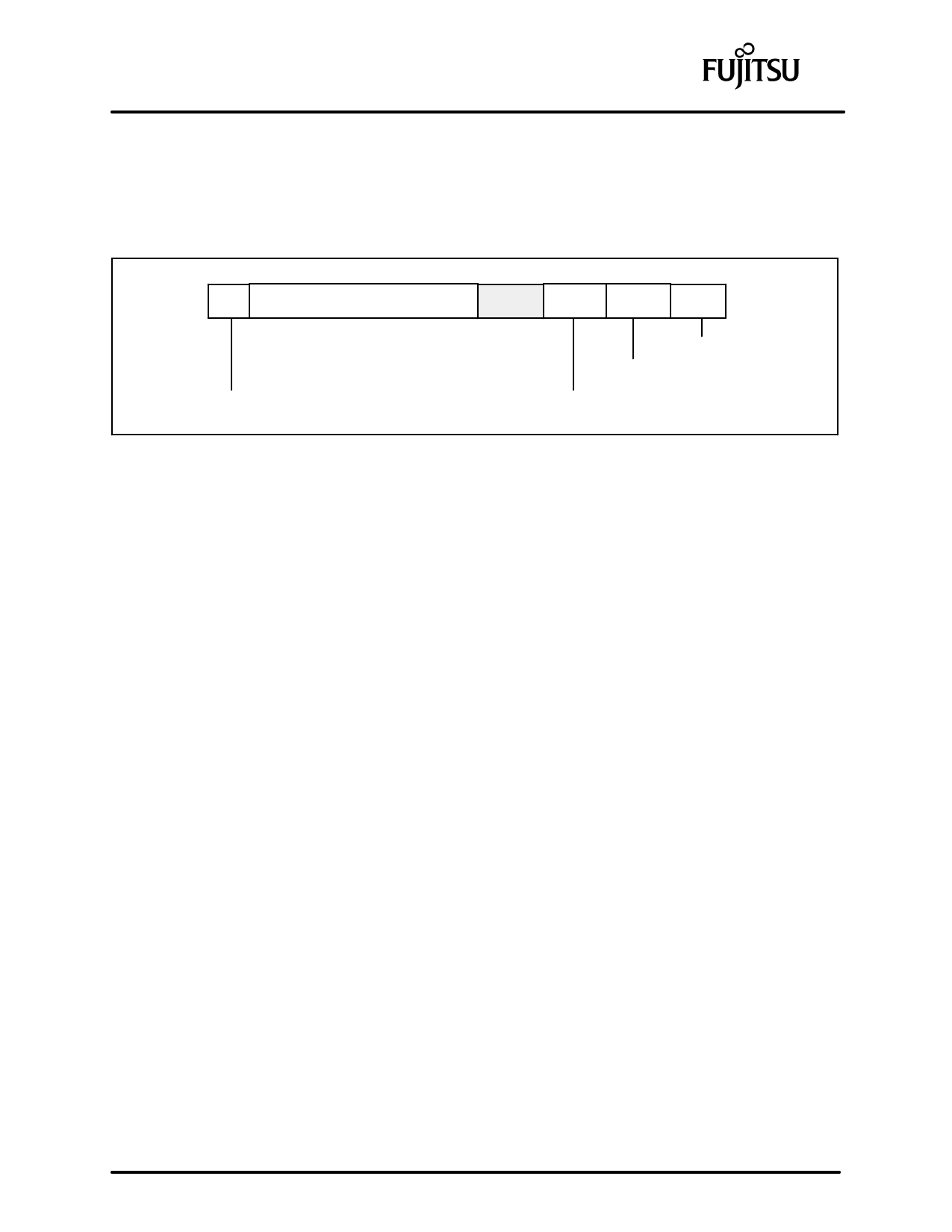

3.2.3. ATRetries

This register sets the retry count when transmitting the asynchronous packet or receiving the “ack_busy_#” or

“ack_data_error” acknowledge. The register performs the retries of the count set here when the received

acknowledge is “ack_busy_#” or “ack_data_error”. “0” are indicated on the secondLimit and the cycleLimit

fields respectively because the MB86613S does not support the dual phase relay.

31

24 23

16 15

cycleLimit

87

0

secondLimit

maxATReqRetries

maxATRespRetries

maxPhyRespRetries

Bit

Field Name

rwu

---- -------------- ----

31:29 secondLimit

r

28:16 cycleLimit

r

reset

--------

0h

000h

description

------------------------------------------

The device supports only single phase retry function. So,

these bits indicate ”0”.

11:8 maxPhyResp

Retries

7:4 maxATResp

Retries

3:0 maxATReq

Retries

rw

undefined Set the retry count for the transmit phy response packet.

rw

undefined Set the retry count for the transmit asynchronous response

packet.

rw

undefined Set the retry count for the transmit asynchronous request

packet.

3.2.4. Bus Management CSR

This register is used for making the device operate the automatic compare- swap for the on- chip bus manage-

ment CSR while the MB86613S device is operating as the resource manager. This register is used as follows:

Store the data that you want to set in the bus management CSR in the csrData. Then, store the data to be

compared with the bus management CSR in the csrCompare. After that, select any of register for the bus

management CSR by csrSel bit. At that time, the csrDone bit is cleared.

With these steps, if the compare- swap is completed, ”1” is indicated in the csrDone bit. At that time, the csrDa-

ta indicate the data previously stored in the bus management CSR which has been selected by the csrSel bit.

This means, if the compare- swap is succeeded, the same data are read out from the csrData and csrCom-

pare. In case the different data are read out from these bits, please set the data read out from the csrData in

the csrCompare and repeat the same steps as above.

Bus reset loads ’3Fh’ to bus_manager_ID register and the following registers value to other three Bus man-

agement CSR registers.

CSR Address

-------------------

”FFFF_F000_021Ch”

”FFFF_F000_0220h”

”FFFF_F000_0224h”

”FFFF_F000_0228h”

csrSel

-----

’00b’

’01b’

’10b’

’11b’

by Bus reset

---------

3Fh

InitialBandwidthAvailable

InitialChannelsAvailableHi

InitialChannelsAbailableLo

description

------------------

bus_manager_ID

bandwidth_available

channels_available_hi

channels_available_lo

28