M37516 Просмотр технического описания (PDF) - Mitsumi

Номер в каталоге

Компоненты Описание

Список матч

M37516 Datasheet PDF : 54 Pages

| |||

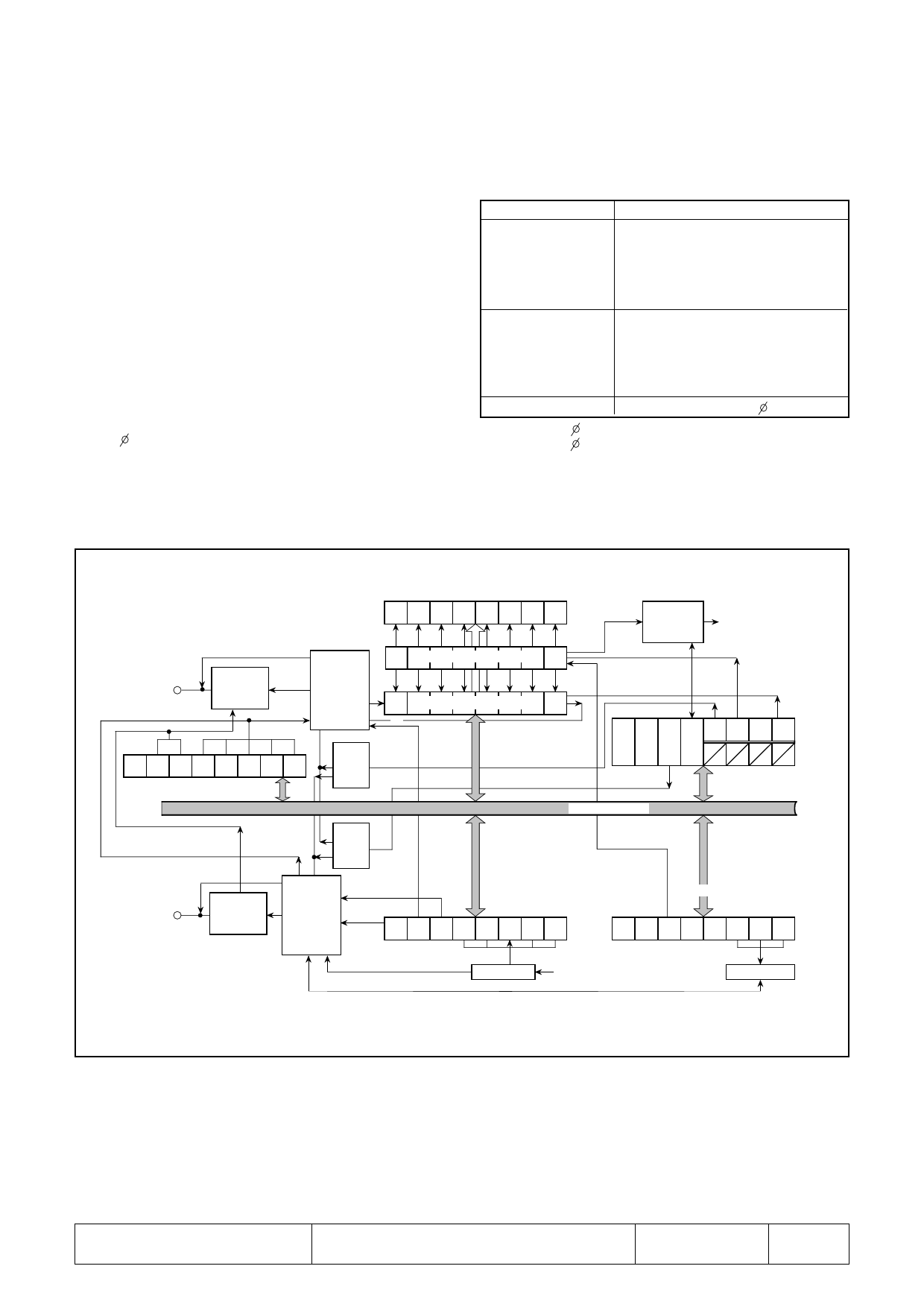

MULTI-MASTER I2C-BUS INTERFACE

The multi-master I2C-BUS interface is a serial communications cir-

cuit, conforming to the Philips I2C-BUS data transfer format. This

interface, offering both arbitration lost detection and a synchro-

nous functions, is useful for the multi-master serial

communications.

Figure 23 shows a block diagram of the multi-master I2C-BUS in-

terface and Table 4 lists the multi-master I2C-BUS interface

functions.

This multi-master I2C-BUS interface consists of the I2C address

register, the I2C data shift register, the I2C clock control register,

the I2C control register, the I2C status register, the I2C start/stop

condition control register and other control circuits.

When using the multi-master I2C-BUS interface, set 1 MHz or

more to .

Note: Mitsubishi Electric Corporation assumes no responsibility for in-

fringement of any third-party’s rights or originating in the use of the

connection control function between the I2C-BUS interface and the

ports SCL1, SCL2, SDA1 and SDA2 with the bit 6 of I2C control regis-

ter (002E16).

Table 4 Multi-master I2C-BUS interface functions

Item

Format

Communication mode

SCL clock frequency

Function

In conformity with Philips I2C-BUS

standard:

10-bit addressing format

7-bit addressing format

High-speed clock mode

Standard clock mode

In conformity with Philips I2C-BUS

standard:

Master transmission

Master reception

Slave transmission

Slave reception

16.1 kHz to 400 kHz (at = 4 MHz)

System clock = f(XIN)/2 (high-speed mode)

= f(XIN)/8 (middle-speed mode)

Serial data

(SDA)

Noise

elimination

circuit

SIS SIP SSC4SSC3 SSC2 SSC1 SSC0

S2D

I2C start/stop condition

control register

b7

I2C address register b0

SAD6 SAD5 SAD4 SAD3 SAD2 SAD1 SAD0 RWB

S0D

Address comparator

Data

control b7

b0

circuit

I2C data shift register

S0

AL

circuit

Interrupt

generating

circuit

Interrupt request signal

(IICIRQ)

b7

b0

AL AAS AD0 LRB

MS TRX BB PIN

T

S1

I2C status register

Internal data bus

BB

circuit

Serial

clock

(SCL)

Noise

elimination

circuit

Clock

control

circuit

I2C clock control register

b7

b0

b7

S1D b0

ACK

ACK FAST

BIT MODE

CCR4 CCR3 CCR2 CCR1 CCR0

S2

I2C clock control register

TISS

TSEL

10BIT

SAD

ALS

ES0 BC2 BC1

BC0

S1D I2C control register

Clock division

System clock (f)

Bit counter

Fig. 23 Block diagram of multi-master I2C-BUS interface

V : Purchase of MITSUBISHI ELECTRIC CORPORATIONS I2C components conveys a license under the Philips I2C Patent Rights to use these components

an I2C system, provided that the system conforms to the I2C Standard Specification as defined by Philips.

M37516M6-XXXHP

GNOK-M37516M6-XXXHP-50

(MSETSU 2)

PA

GE

24/54