IDT74AUC16245PFI Просмотр технического описания (PDF) - Integrated Device Technology

Номер в каталоге

Компоненты Описание

Список матч

IDT74AUC16245PFI Datasheet PDF : 7 Pages

| |||

IDT74AUC16245

1.8V CMOS 16-BIT BUS TRANSCEIVER WITH 3-STATE OUTPUTS

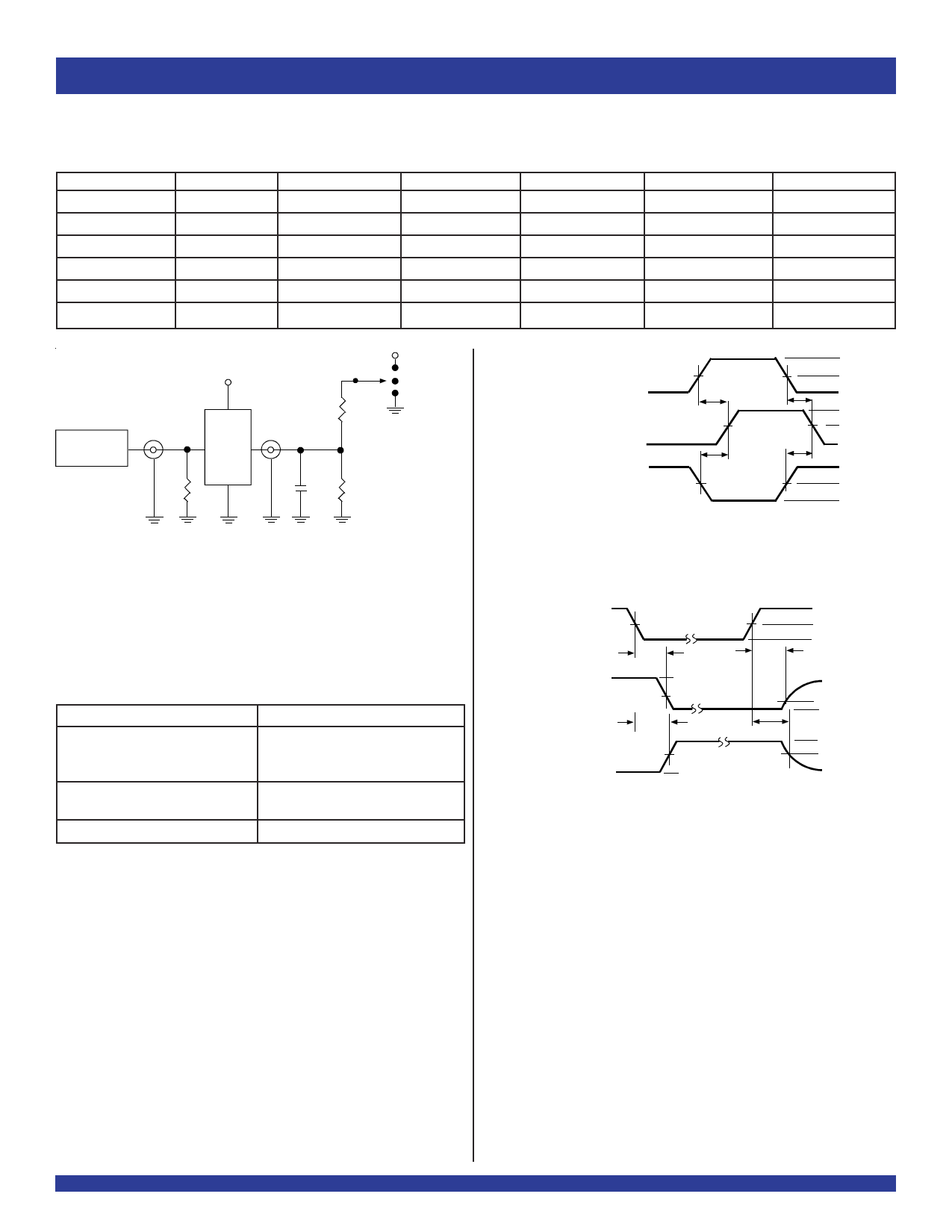

TEST CIRCUITS AND WAVEFORMS

TEST CONDITIONS(1)

Symbol

VDD = 0.8V

VLOAD

2xVDD

VT

VDD/2

VLZ

100

VHZ

100

RL

2

CL

15

VDD = 1.2V±0.1V

2xVDD

VDD/2

100

100

2

15

VDD = 1.5V±0.1V

2xVDD

VDD/2

100

100

2

15

VDD = 1.8V±0.15V

2xVDD

VDD/2

150

150

1

30

INDUSTRIAL TEMPERATURE RANGE

VDD = 2.5V±0.2V

Unit

2xVDD

V

VDD/2

V

150

mV

150

mV

0.5

kΩ

30

pF

VDD

P u ls e(1 )

V IN

Generator

RL

VOUT

D.U.T.

RT

RL

CL

VLOAD

Open

GND

Test Circuits for All Outputs

DEFINITIONS:

CL = Load capacitance: includes jig and probe capacitance.

RT = Termination resistance: should be equal to ZOUT of the Pulse Generator.

NOTE:

1. Pulse Generator for All Pulses: Rate ≤ 10MHz; Slew Rate ≥ 1V/ns.

SWITCH POSITION

Test

Open Drain

Disable Low

Enable Low

Disable High

Enable High

All Other Tests

Switch

VLOAD

GND

Open

SAME PHASE

INPUT TRANSITION

tPLH

OUTPUT

tPLH

OPPOSITE PHASE

INPUT TRANSITION

tPHL

tPHL

VDD

VT

0V

VOH

VT

VOL

VDD

VT

0V

Propagation Delay

CONTROL

INPUT

ENABLE

tPZL

DISABLE

tPLZ

VDD

VT

0V

OUTPUT SWITCH

NORMALLY CLOSED

LOW

tPZH

OUTPUT

SW ITCH

NORMALLY

OPEN

HIGH

V L O AD /2

VT

tPHZ

VT

0V

V L O A D /2

VOL + VLZ

VOL

VOH

VOH - VHZ

0V

NOTE:

1. Diagram shown for input Control Enable-LOW and input Control Disable-HIGH.

Enable and Disable Times

6