LIS331DL Просмотр технического описания (PDF) - STMicroelectronics

Номер в каталоге

Компоненты Описание

Список матч

LIS331DL

LIS331DL Datasheet PDF : 42 Pages

| |||

LIS331DL

Register description

Zen bit enables the generation of Data Ready signal for Z-axis measurement channel when

set to 1. The default value is 1.

Yen bit enables the generation of Data Ready signal for Y-axis measurement channel when

set to 1. The default value is 1.

Xen bit enables the generation of Data Ready signal for X-axis measurement channel when

set to 1. The default value is 1.

7.3

CTRL_REG2 (21h)

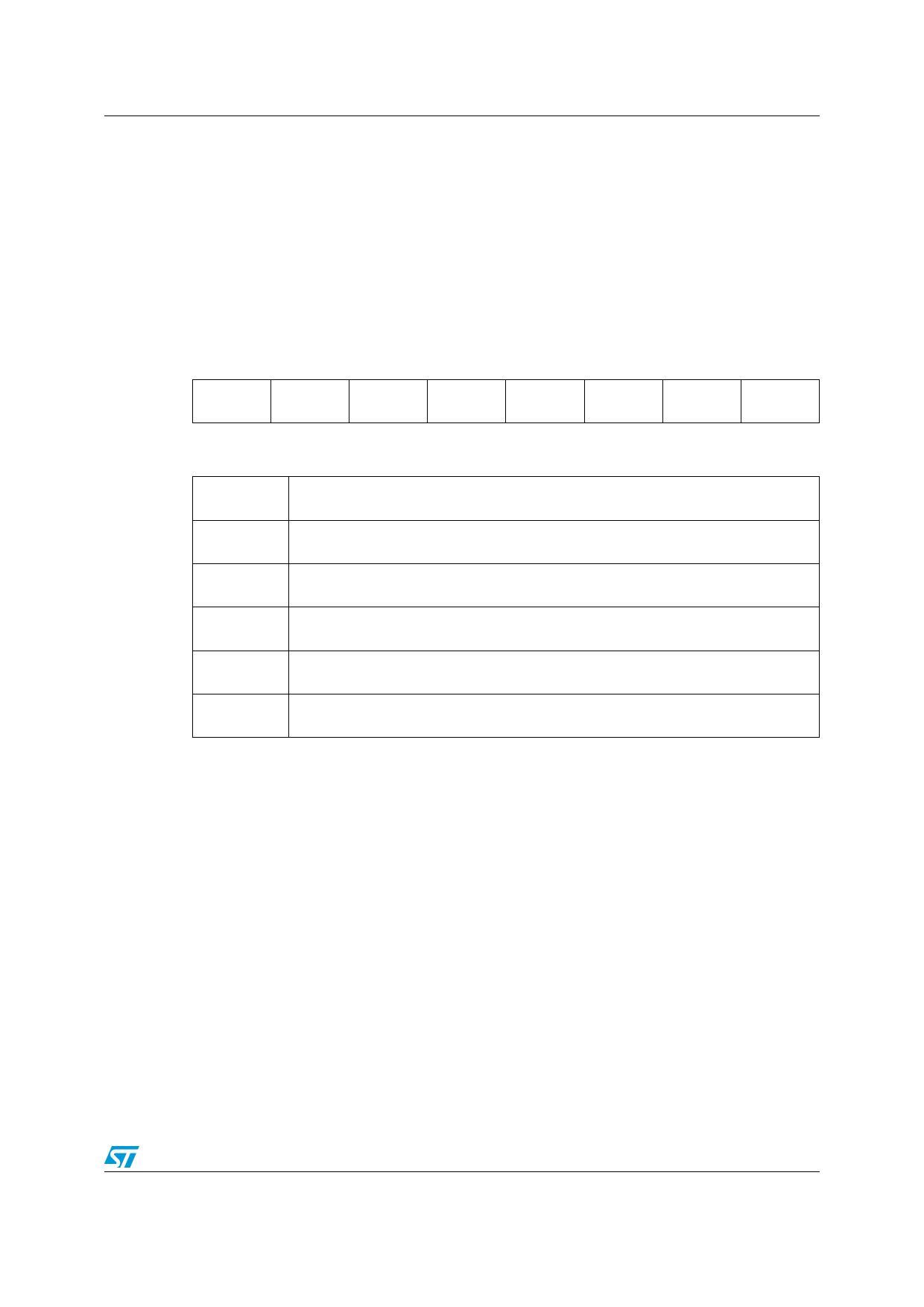

Table 19.

SIM

CTRL_REG2 register

BOOT

0(1)

FDS

HP

FF_WU2

HP

FF_WU1

HPcoeff2

HPcoeff1

1. Bit to be kept to “0” for correct device functionality

Table 20.

SIM

BOOT

FDS

CTRL_REG2 description

SPI Serial Interface Mode selection. Default value: 0

(0: 4-wire interface; 1: 3-wire interface)

Reboot memory content. Default value: 0

(0: normal mode; 1: reboot memory content)

Filtered Data Selection. Default value: 0

(0: internal filter bypassed; 1: data from internal filter sent to output register)

HP

FF_WU2

HP

FF_WU1

HPcoeff2

HPcoeff1

High Pass filter enabled for Free-Fall/WakeUp # 2. Default value: 0

(0: filter bypassed; 1: filter enabled)

High Pass filter enabled for Free-Fall/Wake-Up #1. Default value: 0

(0: filter bypassed; 1: filter enabled)

High pass filter cut-off frequency configuration. Default value: 00

(See Table 21)

SIM bit selects the SPI Serial Interface Mode. When SIM is ‘0’ (default value) the 4-wire

interface mode is selected. The data coming from the device are sent to SDO pad. In 3-wire

interface mode output data are sent to SDA_SDI pad.

BOOT bit is used to refresh the content of internal registers stored in the flash memory

block. At the device power up the content of the flash memory block is transferred to the

internal registers related to trimming functions to permit a good behavior of the device itself.

If for any reason the content of trimming registers was changed it is sufficient to use this bit

to restore correct values. When BOOT bit is set to ‘1’ the content of internal flash is copied

inside corresponding internal registers and it is used to calibrate the device. These values

are factory trimmed and they are different for every accelerometer. They permit a good

behavior of the device and normally they have not to be changed. At the end of the boot

process the BOOT bit is set again to ‘0’.

FDS bit enables (FDS=1) or bypass (FDS=0) the high pass filter in the signal chain of the

sensor

HPcoeff[2:1]. These bits are used to configure high-pass filter cut-off frequency ft.

27/42