ISL97645A Просмотр технического описания (PDF) - Intersil

Номер в каталоге

Компоненты Описание

Список матч

ISL97645A Datasheet PDF : 15 Pages

| |||

ISL97645A

Supply Monitor Circuit

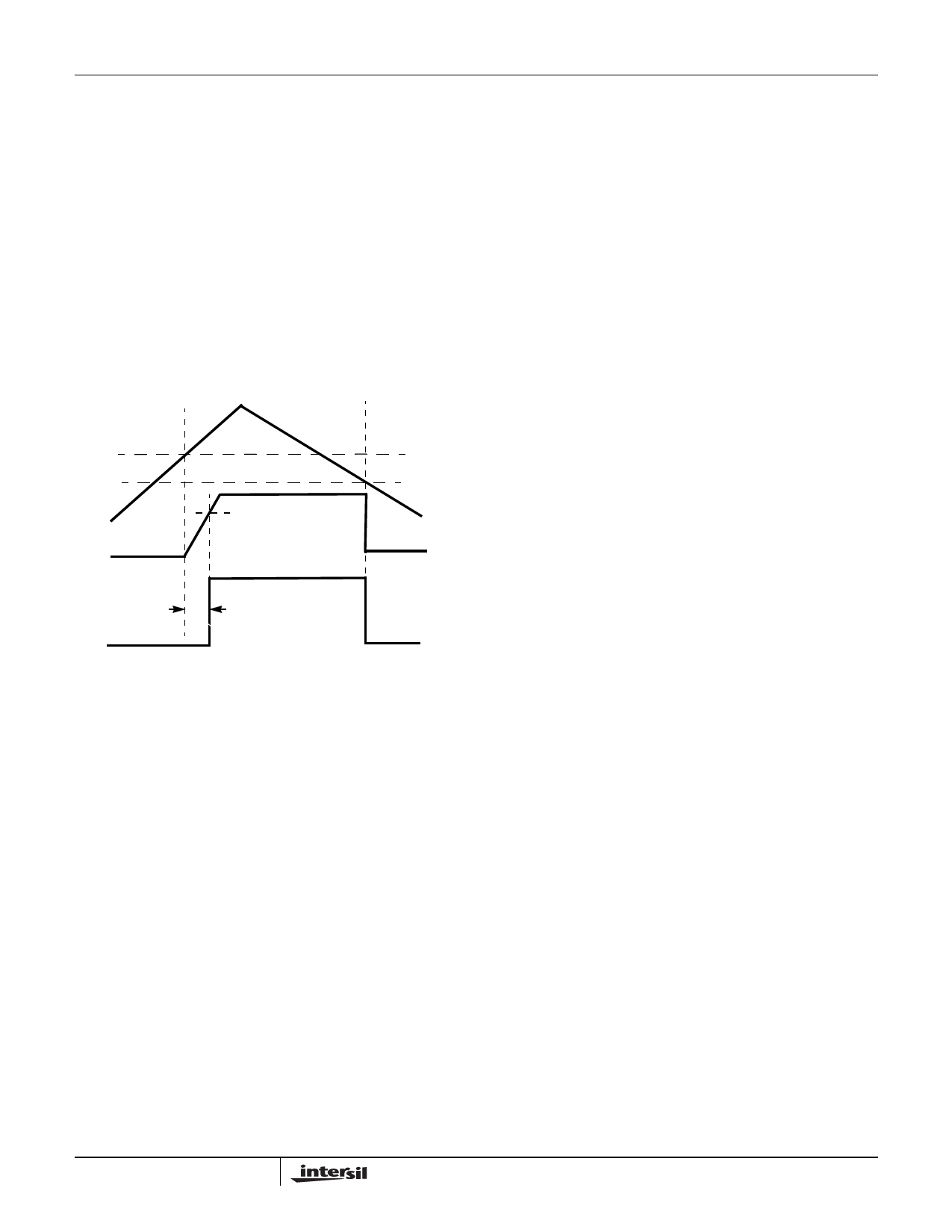

The Supply Monitor circuit monitors the voltage on VDIV,

and sets open-drain output RESET low when VDIV is below

1.15V (rising) or 1.1V (falling).

There is a delay on the rising edge, controlled by a capacitor

on CD2. When VDIV exceeds 1.15V (rising), CD2 is charged

up from 0V to 1.215V by a 10µA current source. Once CD2

exceeds 1.215V, RESET will go tri-state. When VDIV falls

below 1.1V, RESET will become low with a 750 pull-down

resistance. The delay time is controlled by Equation 7:

tdelay = 121.5k × CD2

(EQ. 7)

For example, the delay time is 12.15ms if the CD2 = 100nF.

Figure 15 is the Supply Monitor Circuit timing diagram.

Low to high transition is determined primarily by the switch

resistance and the external capacitive load. High to low

transition is more complex. Take the case where the block is

already enabled (VDPM is H). When VFLK is H, pin CE is

grounded. On the falling edge of VFLK, a current is passed

into pin CE, to charge an external capacitor to 1.2V. This

creates a delay, equal to CE*4200. At this point, the output

begins to pull down from VGH to VDD1. The slew current is

equal to 300/(RE + 5000), and the dv/dt slew rate is

Isl/CLOAD.

where CLOAD is the load capacitance applied to VGHM.

When RESET signal changes to low, and VGH voltage is

above 2.5V, the VGH_M will be tied to VGH voltage until the

VGH voltage falls down to 2.5V. If the VGH voltage is lower

than 2.5V, GPM block will not work properly, and there is no

active control for VGH_M output. The following table shows

the VGH_M status based on Vin, VGH and RESET:

VDIV

CD2

1.215V

1.15V

1.1V

RESET

RESET DELAY TIME IS

CONTROLLED BY CD2

CAPACITOR

FIGURE 15. SUPPLY MONITOR CIRCUIT TIMING DIAGRAM

Gate Pulse Modulator Circuit

The gate pulse modulator circuit functions as a three way

multiplexer, switching VGHM between ground, VDD1 and

VGH. Voltage selection is provided by digital inputs VDPM

(enable) and VFLK (control). High to low delay and slew

control is provided by external components on pins CE and

RE, respectively. A block diagram of the gate pulse

modulator circuit is shown in Figure 16.

When VDPM is LOW, the block is disabled and VGHM is

grounded. When the input voltage exceeds UVLO threshold,

VDPM starts to drive an external capacitor with 20μA. Once

VDPM exceeds 1.215V, the GPM circuit is enabled, and the

output VGH_M is determined by VFLK, RESET signal and

VGH voltage. If RESET signal is high, and when VFLK goes

high, VGHM is pulled to VGH by a 70Ω switch. When VFLK

goes low, there is a delay controlled by capacitor CE,

following which VGHM is driven to VDD1, with a slew rate

controlled by resistor RE. Note that VDD1 is used only as a

reference voltage for an amplifier, thus does not have to

source or sink a significant DC current.

11

FN6353.0

July 2, 2007