HM62V8512BLRR-7UL Просмотр технического описания (PDF) - Hitachi -> Renesas Electronics

Номер в каталоге

Компоненты Описание

Список матч

HM62V8512BLRR-7UL Datasheet PDF : 17 Pages

| |||

HM62V8512B Series

Low VCC Data Retention Characteristics (Ta = –20 to +70°C)

Parameter

Symbol Min Typ Max Unit Test conditions*4

VCC for data retention

Data retention current

VDR

I CCDR

2

—

—V

CS ≥ VCC – 0.2 V, Vin ≥ 0 V

—

0.8*5 20*1 µA

VCC = 3.0 V, Vin ≥ 0 V

CS ≥ VCC – 0.2 V

—

0.8*5 10*2 µA

—

0.8*5 2*3 µA

Chip deselect to data retention time tCDR

0

—

— ns

See retention waveform

Operation recovery time

tR

tRC*6 —

— ns

Notes: 1. For L-version and 10 µA (max.) at Ta = –20 to +40°C.

2. For L-SL-version and 3 µA (max.) at Ta = –20 to +40°C.

3. For L-UL-version and 2 µA (max.) at Ta = –20 to +40°C.

4. CS controls address buffer, WE buffer, OE buffer, and Din buffer. In data retention mode, Vin

levels (address, WE, OE, I/O) can be in the high impedance state.

5. Typical values are at VCC = 3.0 V, Ta = +25°C and specified loading, and not guaranteed.

6. tRC = read cycle time.

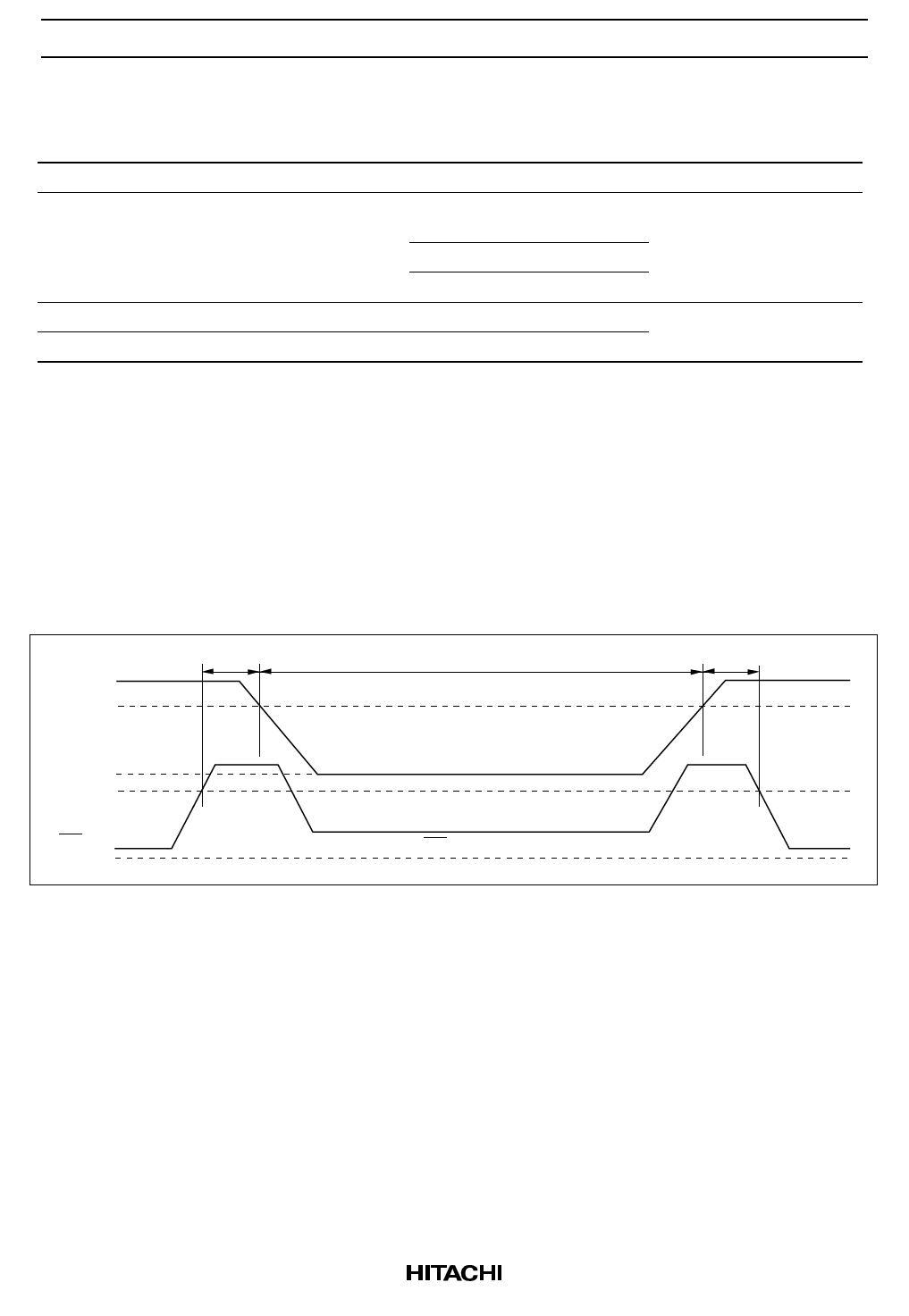

Low VCC Data Retention Timing Waveform (CS Controlled)

t CDR

Data retention mode

tR

VCC

2.7 V

VDR

2.0 V

CS

0V

CS ≥ VCC – 0.2 V

12