IDT72V3643 Просмотр технического описания (PDF) - Integrated Device Technology

Номер в каталоге

Компоненты Описание

Список матч

IDT72V3643

IDT72V3643 Datasheet PDF : 28 Pages

| |||

IDT72V3623/72V3633/72V3643 CMOS 3.3V SyncBiFIFOTM WITH BUS-MATCHING

256 x 36, 512 x 36, 1,024 x 36

COMMERCIAL TEMPERATURE RANGE

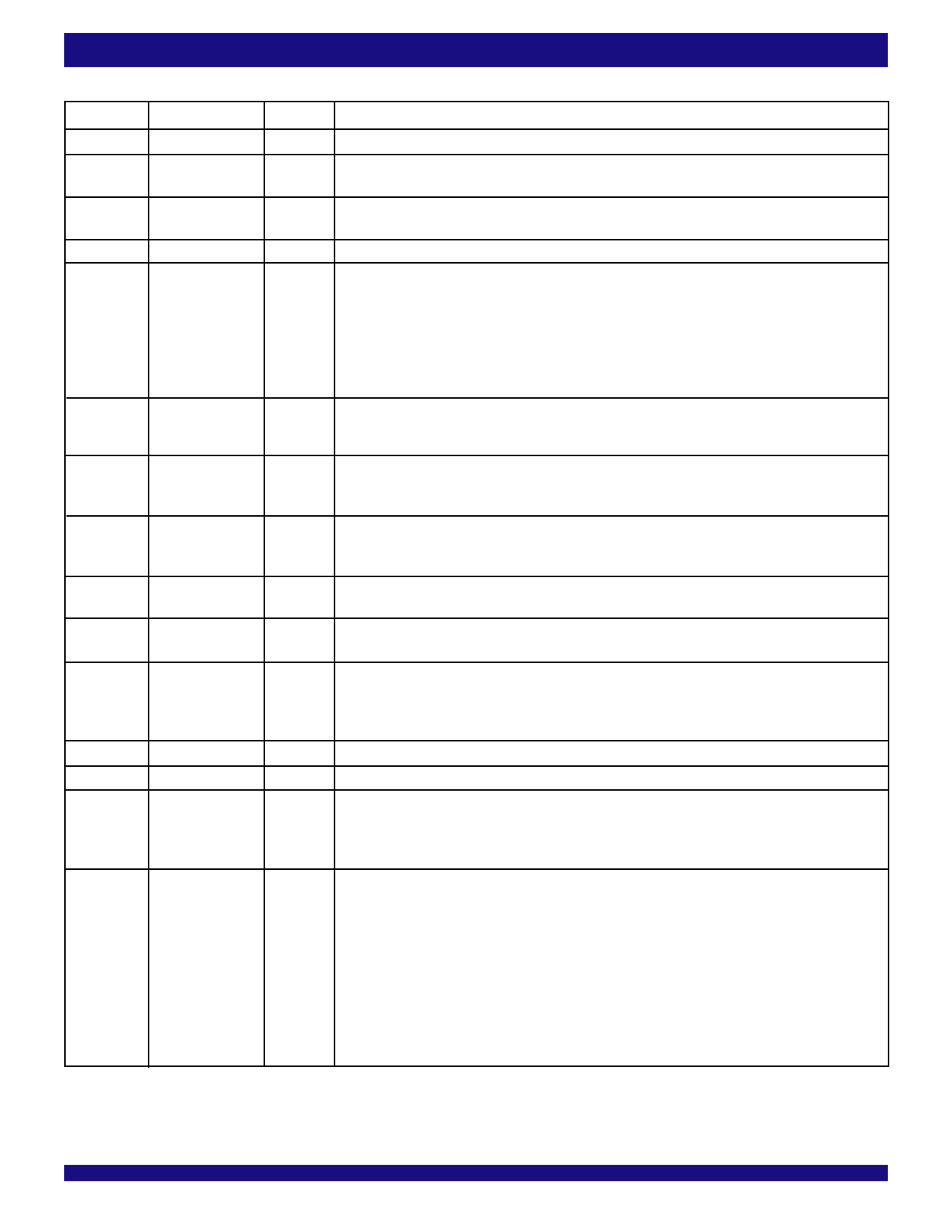

PIN DESCRIPTIONS

Symbol

Name

I/O

Description

A0-A35 Port A Data

I/O 36-bit bidirectional data port for side A.

AE

Almost-Empty Flag

O

Programmable Almost-Empty flag synchronized to CLKB. It is LOW when the number of words in

(Port B)

the FIFO is less than or equal to the value in the Almost-Empty B offset register, X.

AF

Almost-Full Flag

O

Programmable Almost-Full flag synchronized to CLKA. It is LOW when the number of empty

(Port A)

locations in the FIFO is less than or equal to the value in the Almost-Full A offset register, Y.

B0-B35

BE/FWFT

Port B Data

Big-Endian/

First Word

Fall Through

BM

Bus-Match Select

(Port B)

I/O 36-bit bidirectional data port for side B.

I

This is a dual purpose pin. During Master Reset, a HIGH on BE will select Big-Endian operation.

In this case, depending on the bus size, the most significant byte or word written to Port A is read

from Port B first. A LOW on BE will select Little-Endian operation. In this case, the least significant

byte or word written to Port A is read from Port B first. After Master Reset, this pin selects the timing

mode. A HIGH on FWFT selects IDT Standard mode, a LOW selects First Word Fall Through

mode. Once the timing mode has been selected, the level on FWFT must be static throughout

device operation.

I

A HIGH on this pin enables either byte or word bus width on Port B, depending on the state of

SIZE. A LOW selects long word operation. BM works with SIZE and BE to select the bus size and

endian arrangement for Port B. The level of BM must be static throughout device operation.

CLKA

Port A Clock

I

CLKA is a continuous clock that synchronizes all data transfers through Port A and can be

asynchronous or coincident to CLKB. FF/IR and AF are synchronized to the LOW-to-HIGH

transition of CLKA.

CLKB

Port B Clock

CSA

CSB

EF/OR

Port A Chip

Select

Port B Chip

Select

Empty/Output

Ready Flag

(Port B)

I

CLKB is a continuous clock that synchronizes all data transfers through Port B and can be

asynchronous or coincident to CLKA. EF/OR and AE are synchronized to the LOW-to-HIGH

transition of CLKB.

I

CSA must be LOW to enable to LOW-to-HIGH transition of CLKA to read or write on Port A. The

A0-A35 outputs are in the high-impedance state when CSA is HIGH.

I

CSB must be LOW to enable a LOW-to-HIGH transition of CLKB to read or write data on Port B.

The B0-B35 outputs are in the high-impedance state when CSB is HIGH.

O This is a dual function pin. In the IDT Standard mode, the EF function is selected. EFindicates

whether or not the FIFO memory is empty. In the FWFT mode, the OR function is selected. OR indicates

the presence of valid data on the B0-B35 outputs, available for reading. EF/OR is synchronized to the

LOW-to-HIGH transition of CLKB.

ENA

Port A Enable

I

ENA must be HIGH to enable a LOW-to-HIGH transition of CLKA to read or write data on Port A.

ENB

FF/IR

FS1/SEN

FS0/SD

Port B Enable

Full/Input

Ready Flag

(Port A)

Flag Offset

Select 1/

Serial Enable,

Flag Offset

Select 0/

Serial Data

I

ENB must be HIGH to enable a LOW-to-HIGH transition of CLKB to read or write data on Port B.

O

This is a dual function pin. In the IDT Standard mode, the FF function is selected. FF indicates

whether or not the FIFO memory is full. In the FWFT mode, the IR function is selected. IR

indicates whether or not there is space available for writing to the FIFO memory. FF/IR is

synchronized to the LOW-to-HIGH transition of CLKA.

I FS1/SEN and FS0/SD are dual-purpose inputs used for flag offset register programming. During

Reset, FS1/SEN and FS0/SD, together with SPM, select the flag offset programming method.

Three offset register programming methods are available: automatically load one of three preset

values (8, 16, or 64), parallel load from Port A, and serial load.

I

When serial load is selected for flag offset register programming, FS1/SEN is used as an enable

synchronous to the LOW-to-HIGH transition of CLKA. When FS1/SEN is LOW, a rising edge on CLKA

CLKA load the bit present on FS0/SD into the X and Y registers. The number of bit writes required

to program the offset registers is 16 for the IDT72V3623, 18 for the IDT72V3633, and 20 for the

IDT72V3643. The first bit write stores the Y-register MSB and the last bit write stores the X-register LSB.

4