IDT72T36125L5BBI Просмотр технического описания (PDF) - Integrated Device Technology

Номер в каталоге

Компоненты Описание

Список матч

IDT72T36125L5BBI

IDT72T36125L5BBI Datasheet PDF : 57 Pages

| |||

IDT72T3645/55/65/75/85/95/105/115/125 2.5V TeraSync 36-BIT FIFO

1K x 36, 2K x 36, 4K x 36, 8K x 36, 16K x 36, 32K x 36, 64K x 36, 128K x 36 and 256K x 36

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

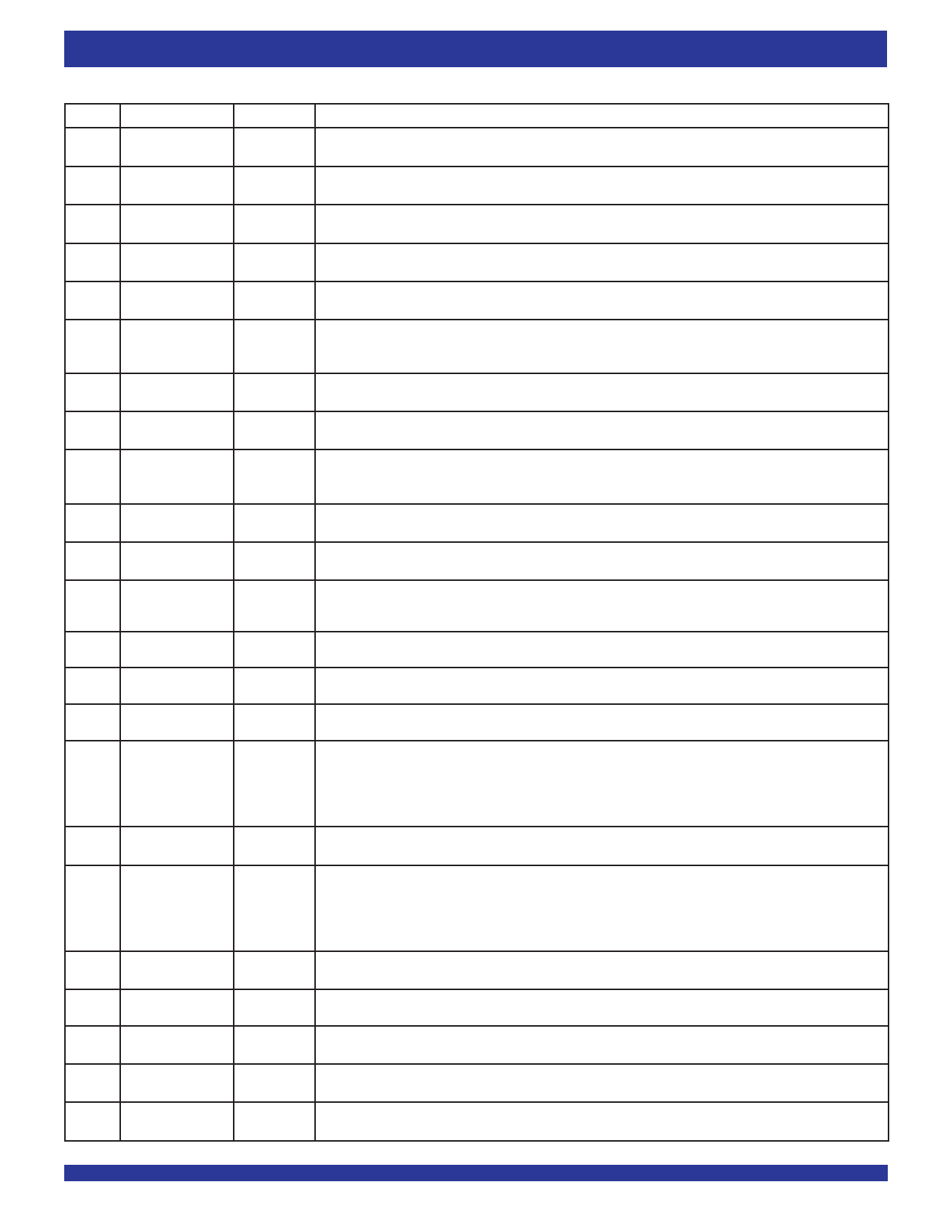

PIN DESCRIPTION

Symbol Name

I/O TYPE

Description

ASYR(1) Asynchronous

Read Port

ASYW(1) Asynchronous

Write Port

BE(1) Big-Endian/

Little-Endian

BM(1) Bus-Matching

D0–D35 DataInputs

EF/OR Empty Flag/

Output Ready

LVTTL A HIGH on this input during Master Reset will select Synchronous read operation for the output port. A LOW

INPUT willselectAsynchronousoperation.IfAsynchronousisselectedtheFIFOmustoperateinIDTStandardmode.

LVTTL A HIGH on this input during Master Reset will select Synchronous write operation for the input port. A LOW

INPUT will select Asynchronous operation.

LVTTL During Master Reset, a LOW on BE will select Big-Endian operation. A HIGH on BE during Master Reset

INPUT will select Little-Endian format.

LVTTL BM works with IW and OW to select the bus sizes for both write and read ports. See Table 1 for bus size

INPUT configuration.

HSTL-LVTTL Data inputs for a 36-, 18- or 9-bit bus. When in 18- or 9-bit mode, the unused input pins should be tied to GND.

INPUT

HSTL-LVTTL IntheIDTStandardmode,theEFfunctionisselected.EFindicateswhetherornottheFIFOmemoryisempty.

OUTPUT In FWFT mode, the OR function is selected. OR indicates whether or not there is valid data available at the

outputs.

ERCLK RCLK Echo

HSTL-LVTTL Read clock Echo output, only available when the Read is setup for Synchronous mode.

OUTPUT

EREN Read Enable Echo HSTL-LVTTL Read Enable Echo output, only available when the Read is setup for Synchronous mode.

OUTPUT

FF/IR Full Flag/

Input Ready

HSTL-LVTTL In the IDT Standard mode, the FF function is selected. FF indicates whether or not the FIFO memory is

OUTPUT full. In the FWFT mode, the IR function is selected. IR indicates whether or not there is space available for

writing to the FIFO memory.

FSEL0(1) Flag Select Bit 0

LVTTL During Master Reset, this input along with FSEL1 and the LD pin, will select the default offset values for the

INPUT programmable flags PAE and PAF. There are up to eight possible settings available.

FSEL1(1) Flag Select Bit 1

LVTTL During Master Reset, this input along with FSEL0 and the LD pin will select the default offset values for the

INPUT programmable flags PAE and PAF. There are up to eight possible settings available.

FWFT/ First Word Fall HSTL-LVTTL During Master Reset, selects First Word Fall Through or IDT Standard mode. After Master Reset, this pin

SI

Through/Serial In INPUT functions as a serial input for loading offset registers. If Asynchronous operation of the read port has been

selected then the FIFO must be set-up in IDT Standard mode.

HF Half-Full Flag

HSTL-LVTTL HF indicates whether the FIFO memory is more or less than half-full.

OUTPUT

IP(1) Interspersed Parity LVTTL During Master Reset, a LOW on IP will select Non-Interspersed Parity mode. A HIGH will select Interspersed

INPUT Parity mode.

IW(1) InputWidth

LVTTL Thispin,alongwithOWandBM,selectsthebuswidthofthewriteport.SeeTable1forbussizeconfiguration.

INPUT

LD

Load

HSTL-LVTTL This is a dual purpose pin. During Master Reset, the state of the LD input along with FSEL0 and FSEL1,

INPUT determinesoneofeightdefaultoffsetvaluesforthePAE andPAFflags,alongwiththemethodbywhichthese

offset registers can be programmed, parallel or serial (see Table 2). After Master Reset, this pin enables writing

to and reading from the offset registers.THIS PIN MUST BE HIGH AFTER MASTER RESET TO WRITE

OR READ DATA TO/FROM THE FIFO MEMORY.

MARK

MRS

OE

OW(1)

PAE

PAF

PFM(1)

MarkforRetransmit HSTL-LVTTL When this pin is asserted the current location of the read pointer will be marked. Any subsequent Retransmit

INPUT operation will reset the read pointer to this position.

Master Reset

HSTL-LVTTL MRS initializes the read and write pointers to zero and sets the output register to all zeroes. During Master

INPUT Reset, the FIFO is configured for either FWFT or IDT Standard mode, Bus-Matching configurations,

Synchronous/Asynchronous operation of the read or write port, one of eight programmable flag default settings,

serial or parallel programming of the offset settings, Big-Endian/Little-Endian format, zero latency timing mode,

interspersed parity, and synchronous versus asynchronous programmable flag timing modes.

Output Enable

HSTL-LVTTL OE provides Asynchronous three-state control of the data outputs, Qn. During a Master or Partial Reset the

INPUT OE input is the only input that provide High-Impedance control of the data outputs.

Output Width

Programmable

Almost-Empty Flag

LVTTL This pin, along with IW and BM, selects the bus width of the read port. See Table 1 for bus size configuration.

INPUT

HSTL-LVTTL PAEgoes LOW if the number of words in the FIFO memory is less than offset n, which is stored in the Empty

OUTPUT Offsetregister.PAE goesHIGHifthenumberofwordsintheFIFOmemoryisgreaterthanorequalto offsetn.

Programmable

HSTL-LVTTL PAFgoes HIGH if the number of free locations in the FIFO memory is more than offset m, which is stored in the

Almost-Full Flag

OUTPUT Full Offsetregister.PAFgoesLOWifthenumberoffreelocationsintheFIFOmemoryislessthanorequaltom.

Programmable

Flag Mode

LVTTL During Master Reset, a LOW on PFM will select Asynchronous Programmable flag timing mode. A HIGH on

INPUT PFM will select Synchronous Programmable flag timing mode.

7