HCF4035 Просмотр технического описания (PDF) - STMicroelectronics

Номер в каталоге

Компоненты Описание

Список матч

HCF4035 Datasheet PDF : 14 Pages

| |||

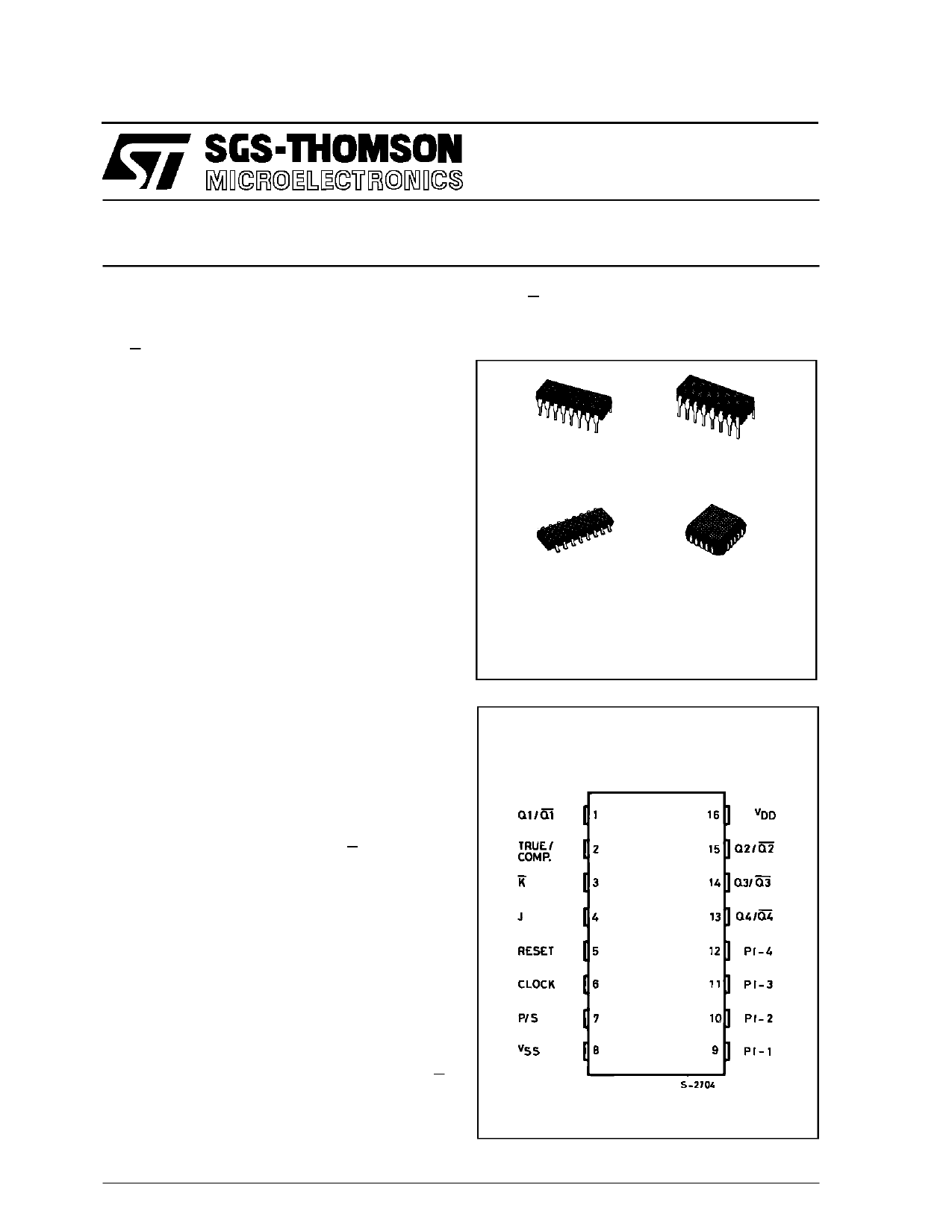

HCC/HCF4035B

4-STAGE PARALLEL IN/PARALLEL OUT SHIFT REGISTER

. 4-STAGE CLOCKED SHIFT OPERATION

. SYNCHRONOUS PARALLEL ENTRY ON ALL 4

STAGES

. JK INPUTS ON FIRST STAGE

. ASYNCHRONOUS TRUE/COMPLEMENT CON-

TROL ON ALL OUTPUTS

. STATIC FLIP-FLOP OPERATION ; MASTER-

SLAVE CONFIGURATION

. BUFFERED INPUTS AND OUTPUTS

. HIGH SPEED 12MHz (typ.) AT VDD = 10V

. QUIESCENT CURRENT SPECIFIED TO 20V

FOR HCC DEVICE

. STANDARDIZED SYMMETRICAL OUTPUT

CHARACTERISTICS

. 5V, 10V, AND 15V PARAMETRIC RATINGS

. INPUT CURR 100nA AT 18V AND 25°C FOR

HCC DEVICE

. 100% TESTED FOR QUIESCENT CURRENT

. MEETS ALL REQUIREMENTS OF JEDECTEN-

TATIVE STANDARD N°. 13A, ”STANDARD

SPECIFICATIONS FOR DESCRIPTION OF ”B”

SERIES CMOS DEVICES”

Whith JK inputs connected together, the first stage

becomes a D flip-flop. An asynchronous common

RESET is also provided.

EY

F

(Plastic Package) (Ceramic Frit Seal Package)

M1

(Micro Package)

C1

(Plastic Chip Carrier)

ORDER CODES :

HCC4035BF

HCF4035BM1

HC F 40 35B EY

HCF4035BC1

DESCRIPTION

The HCC4035B (extended temperature range) and

HCF4035B (intermediate temperature range) are

monolithic integrated circuit, available in 16-lead

dual in-line plastic or ceramic package and plastic

micro package. The HCC/HCF4035B is a four-

stage clocked signal serial register with provision for

synchronous PARALLEL inputs to each stage and

SERIAL inputs to the first stage via JK logic. Regis-

ter stages 2, 3, and 4 are coupled in a serial D flip-

flop configuration when the register is in the serial

mode (PARALLEL/SERIAL control low). Parallel

entry into each register stage is permitted when the

PARALLEL/SERIAL control is high. In the parallel or

serial mode information is transferred on positive

clock transitions. When the TRUE/COMPLEMENT

control is high, the true contents of the register are

available at the output terminals. When the

TRUE/COMPLEMENT control is low, the outputs

are the complements of the data in the register. The

TRUE/COMPLEMENT control functions asyn-

chronously with respect to the CLOCK signal. JK

input logic is provided on the first stage SERIAL

input to minimize logic requirements particularly in

counting and sequence-generation applications.

PIN CONNECTIONS

July 1989

1/14