CS5351-KS Просмотр технического описания (PDF) - Cirrus Logic

Номер в каталоге

Компоненты Описание

Список матч

CS5351-KS Datasheet PDF : 24 Pages

| |||

CS5351

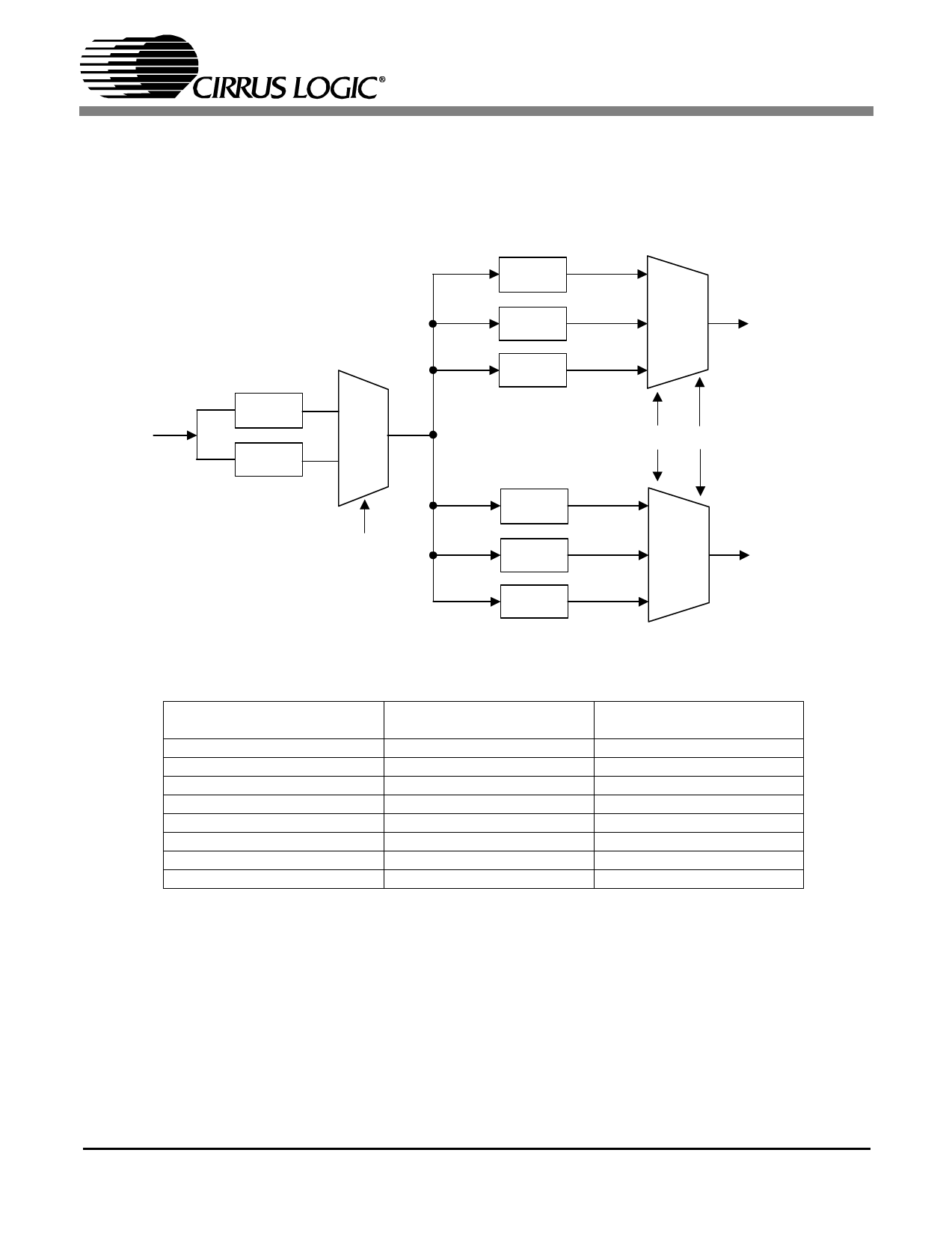

3.2.1 Master Mode

In Master mode, LRCK and SCLK operate as outputs. The left/right and serial clocks are internally derived

from the master clock with the left/right clock equal to Fs and the serial clock equal to 64x Fs, as shown

in Figure 2. Refer to Table 2 for common master clock frequencies

MCLK

÷1

0

÷2

1

MDIV

÷ 256

Single

Speed

00

÷ 128

Double

Speed

01

÷ 64

Quad

Speed

10

LRCK Output

(Equal to Fs)

M1 M0

÷4

Single

Speed

00

÷2

Double

Speed

01

÷1

Quad

Speed

10

SCLK Output

Figure 2. CS5351 Master Mode Clocking

SAMPLE RATE (kHz)

32

44.1

48

64

88.2

96

176.4

192

MDIV = 0

MCLK (MHz)

8.192

11.2896

12.288

8.192

11.2896

12.288

11.2896

12.288

MDIV = 1

MCLK (MHz)

16.384

22.5792

24.576

16.384

22.5792

24.576

22.5792

24.576

Table 2. CS5351 Common Master Clock Frequencies

DS565PP2

7