CS4361 Просмотр технического описания (PDF) - Cirrus Logic

Номер в каталоге

Компоненты Описание

Список матч

CS4361 Datasheet PDF : 24 Pages

| |||

Confidential Draft

2/12/08

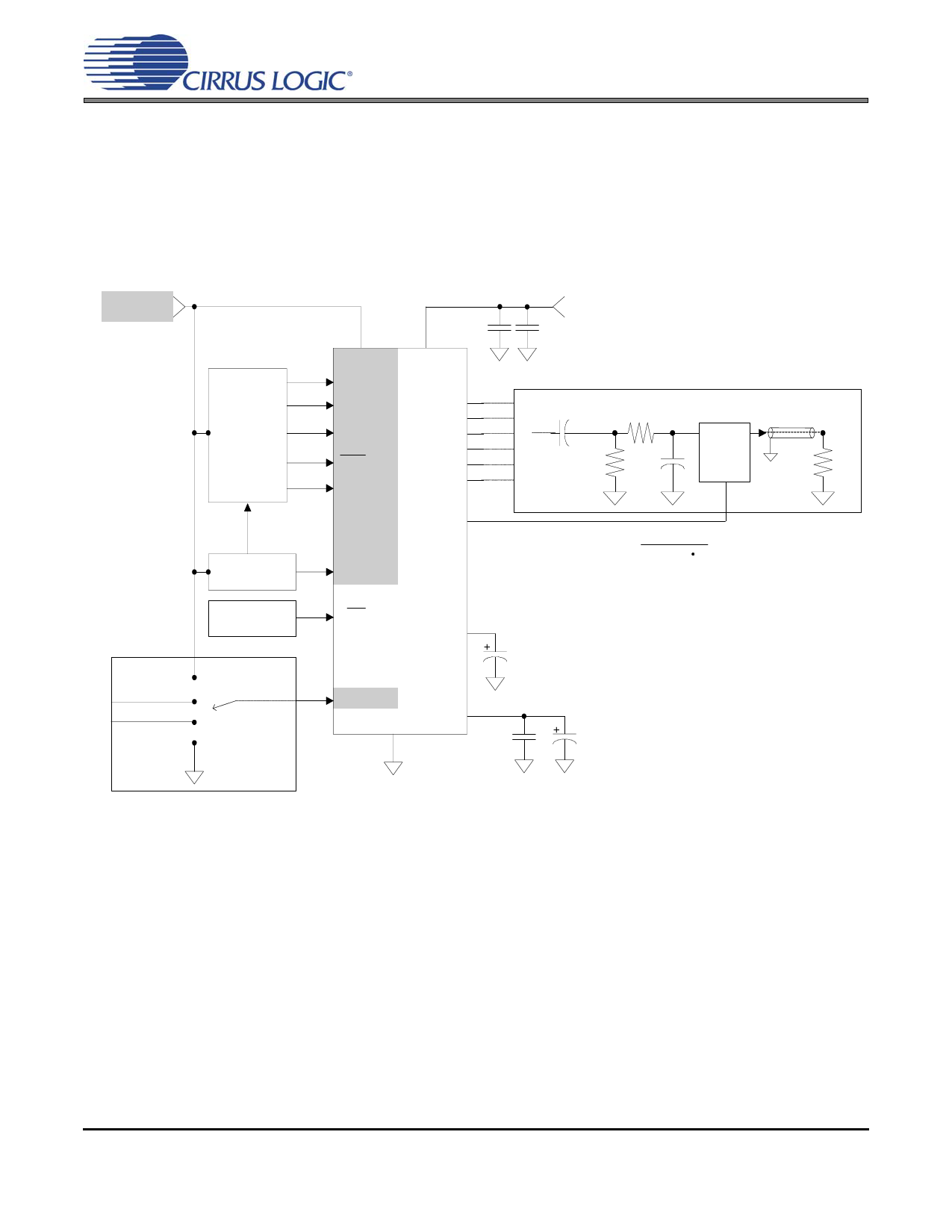

3. TYPICAL CONNECTION DIAGRAM

CS4361

+1.8 V to +5 V

Audio

Data

Processor

External Clock

µControler

VL I2S

LRCK RJ24

MCLK

RJ16

GND LJ

1

VL

2 SDIN1

3 SDIN2

4 SDIN3

5 DEM/SCLK

6 LRCK

0.1 µF

15

VA

AOUT1 19

AOUT2 18

AOUT3 17

AOUT4 16

AOUT5 13

AOUT6 12

MUTEC 20

CS4361

7

MCLK

8

RST

10

FILT+

+5 V

+

1 µF

Note*

3.3 µF

470Ω Audio Output

+

Optional

Muting

10 kΩ

C Circuit

Rext

Note* = This circuitry is iCnte=nd4eRπdFefxsot(rR+ae4px7pt 0lic4a7ti0o)nFsorwbheesrte2th0ekHCzS4re3s6p1ocnosnenects

directly to an unbalanced output of the design. For internal routing

applications please see the DAC analog output characteristics for loading

limitations.

33 µF

9 MODE

GND

14

VQ 11

0.1 µF

*3.3 µF *Popguard ramp can be adjusted by selecting

or this capacitor value to be 3.3 µF to give 250 ms

*10µF ramp time or 10 µF to give a 420 ms ramp time.

Figure 6. Recommended Connection Diagram

11