IDT72V04(1996) Просмотр технического описания (PDF) - Integrated Device Technology

Номер в каталоге

Компоненты Описание

Список матч

IDT72V04

(Rev.:1996)

(Rev.:1996)

IDT72V04 Datasheet PDF : 13 Pages

| |||

IDT72V01/72V02/72V03/72V04 3.3 VOLT CMOS ASYNCHRONOUS FIFO

512 x 9, 1,024 x 9, 2,048 x 9, 4,096 x 9

AC TEST CONDITIONS

Input Pulse Levels

Input Rise/Fall Times

Input Timing Reference Levels

Output Reference Levels

Output Load

GND to 3.0V

5ns

1.5V

1.5V

See Figure 1

2679 tbl 08

COMMERCIAL TEMPERATURE RANGE

5.0V

TO

OUTPUT

PIN

680Ω

1.1K

30pF*

2679 drw 03

or equivalent circuit

Figure 1. Output Load

* Includes scope and jig capacitances.

SIGNAL DESCRIPTIONS

INPUTS:

DATA IN (D0 – D8)

Data inputs for 9-bit wide data.

CONTROLS:

RESET (RS)

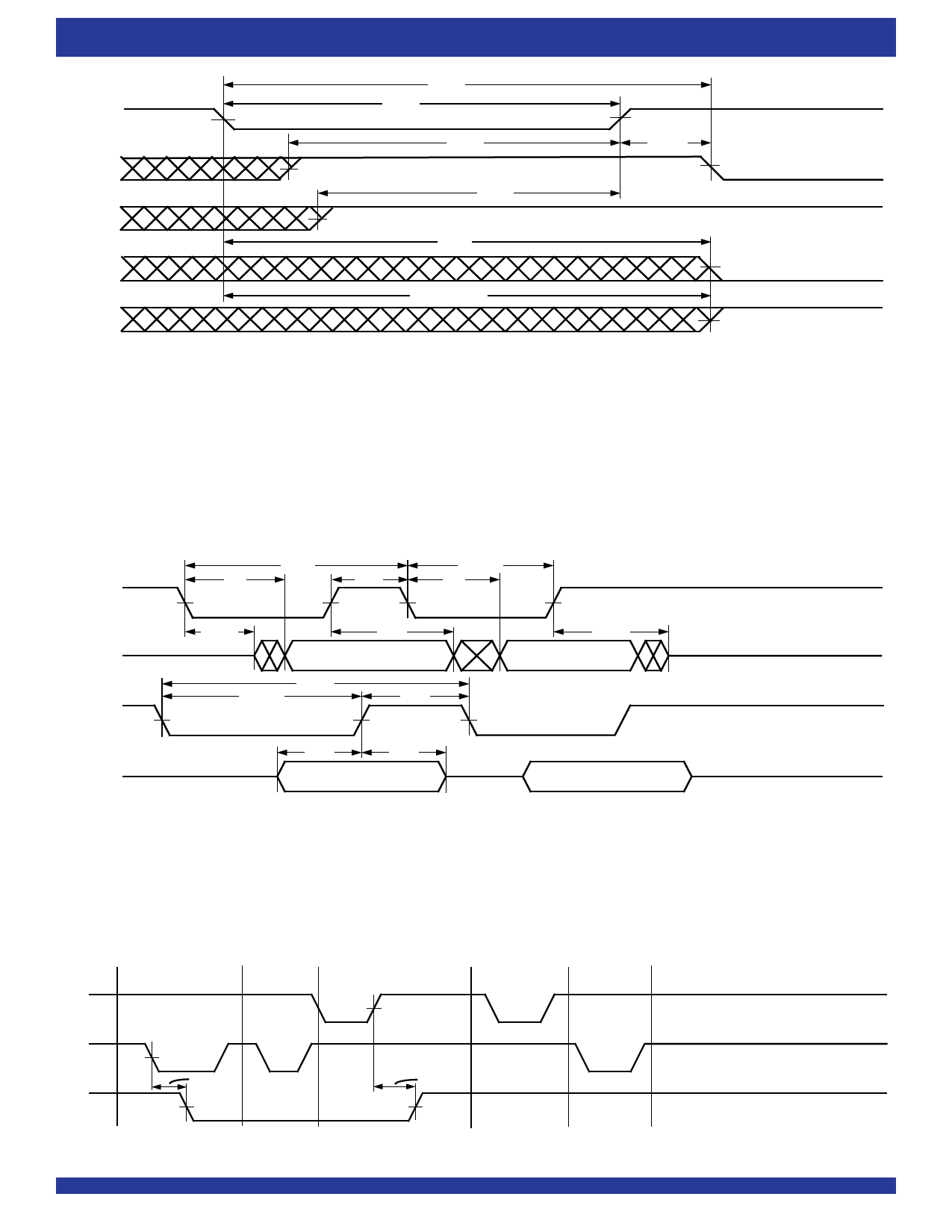

Reset is accomplished whenever the Reset (RS) input is

taken to a low state. During reset, both internal read and write

pointers are set to the first location. A reset is required after

power up before a write operation can take place. Both the

Read Enable (R) and Write Enable (W) inputs must be in

the high state during the window shown in Figure 2, (i.e.,

tRSS before the rising edge of RS) and should not change

until tRSR after the rising edge of RS. Half-Full Flag (HF)

will be reset to high after Reset (RS).

WRITE ENABLE (W)

A write cycle is initiated on the falling edge of this input if the

Full Flag (FF) is not set. Data set-up and hold times must be

adhered to with respect to the rising edge of the Write Enable

(W). Data is stored in the RAM array sequentially and

independently of any on-going read operation.

After half of the memory is filled and at the falling edge of

the next write operation, the Half-Full Flag (HF) will be set to

low and will remain set until the difference between the write

pointer and read pointer is less than or equal to one half of the

total memory of the device. The Half-Full Flag (HF) is then

reset by the rising edge of the read operation.

To prevent data overflow, the Full Flag (FF) will go low,

inhibiting further write operations. Upon the completion of a

valid read operation, the Full Flag (FF) will go high after tRFF,

allowing a valid write to begin. When the FIFO is full, the

internal write pointer is blocked from W, so external changes

in W will not affect the FIFO when it is full.

READ ENABLE (R)

A read cycle is initiated on the falling edge of the Read

Enable (R) provided the Empty Flag (EF) is not set. The data

is accessed on a First-In/First-Out basis, independent of any

ongoing write operations. After Read Enable (R) goes high,

the Data Outputs (Q0 – Q8) will return to a high impedance

condition until the next Read operation. When all data has

been read from the FIFO, the Empty Flag (EF) will go low,

allowing the “final” read cycle but inhibiting further read

operations with the data outputs remaining in a high imped-

ance state. Once a valid write operation has been accom-

plished, the Empty Flag (EF) will go high after tWEF and a valid

Read can then begin. When the FIFO is empty, the internal

read pointer is blocked from R so external changes in R will not

affect the FIFO when it is empty.

FIRST LOAD/RETRANSMIT (FL/RT)

This is a dual-purpose input. In the Depth Expansion Mode,

this pin is grounded to indicate that it is the first loaded (see

Operating Modes). In the Single Device Mode, this pin acts as

the restransmit input. The Single Device Mode is initiated by

grounding the Expansion In (XI).

The IDT72V01/72V02/72V03/72V04 can be made to re-

transmit data when the Retransmit Enable control (RT) input

is pulsed low. A retransmit operation will set the internal read

pointer to the first location and will not affect the write pointer.

Read Enable (R) and Write Enable (W) must be in the high

state during retransmit. This feature is useful when less than

512/1024/2048/4096 writes are performed between resets.

The retransmit feature is not compatible with the Depth

Expansion Mode and will affect the Half-Full Flag (HF), de-

pending on the relative locations of the read and write point-

ers.

EXPANSION IN (XI)

This input is a dual-purpose pin. Expansion In (XI) is

grounded to indicate an operation in the single device mode.

Expansion In (XI) is connected to Expansion Out (XO) of the

previous device in the Depth Expansion or Daisy Chain Mode.

OUTPUTS:

FULL FLAG (FF)

The Full Flag (FF) will go low, inhibiting further write op-

eration, when the write pointer is one location less than the

read pointer, indicating that the device is full. If the read

pointer is not moved after Reset (RS), the Full-Flag (FF) will go

5.08

5