AD9245 Просмотр технического описания (PDF) - Analog Devices

Номер в каталоге

Компоненты Описание

Список матч

AD9245 Datasheet PDF : 32 Pages

| |||

AD9245

SWITCHING SPECIFICATIONS

AVDD = 3 V, DRVDD = 2.5 V, unless otherwise noted.

Table 6.

Parameter

CLOCK INPUT PARAMETERS

Maximum Conversion Rate

Minimum Conversion Rate

CLK Period

CLK Pulse Width High1

CLK Pulse Width Low1

DATA OUTPUT PARAMETERS

Output Delay2 (tPD)

Pipeline Delay (Latency)

Aperture Delay (tA)

Aperture Uncertainty Jitter (tJ)

Wake-Up Time3

OUT-OF-RANGE RECOVERY TIME

AD9245BCP-20

Min Typ Max

20

1

50.0

15.0

15.0

3.5

7

1.0

0.5

3.0

1

AD9245BCP-40

Min Typ Max

40

1

25.0

8.8

8.8

3.5

7

1.0

0.5

3.0

1

AD9245BCP-65

Min Typ Max

65

1

15.4

6.2

6.2

3.5

7

1.0

0.5

3.0

2

AD9245BCP-80

Min Typ Max

80

1

12.5

4.6

4.6

4.2

7

1.0

0.3

7.0

2

Unit

MSPS

MSPS

ns

ns

ns

ns

Cycles

ns

ps rms

ms

Cycles

1 For the AD9245BCP-65 and AD9245BCP-80 models only, with duty cycle stabilizer enabled. DCS function not applicable for AD9245BCP-20 and AD9245BCP-40

models.

2 Output delay is measured from CLK 50% transition to DATA 50% transition, with 5 pF load on each output.

3 Wake-up time is dependent on value of decoupling capacitors; typical values shown with 0.1 μF and 10 μF capacitors on REFT and REFB.

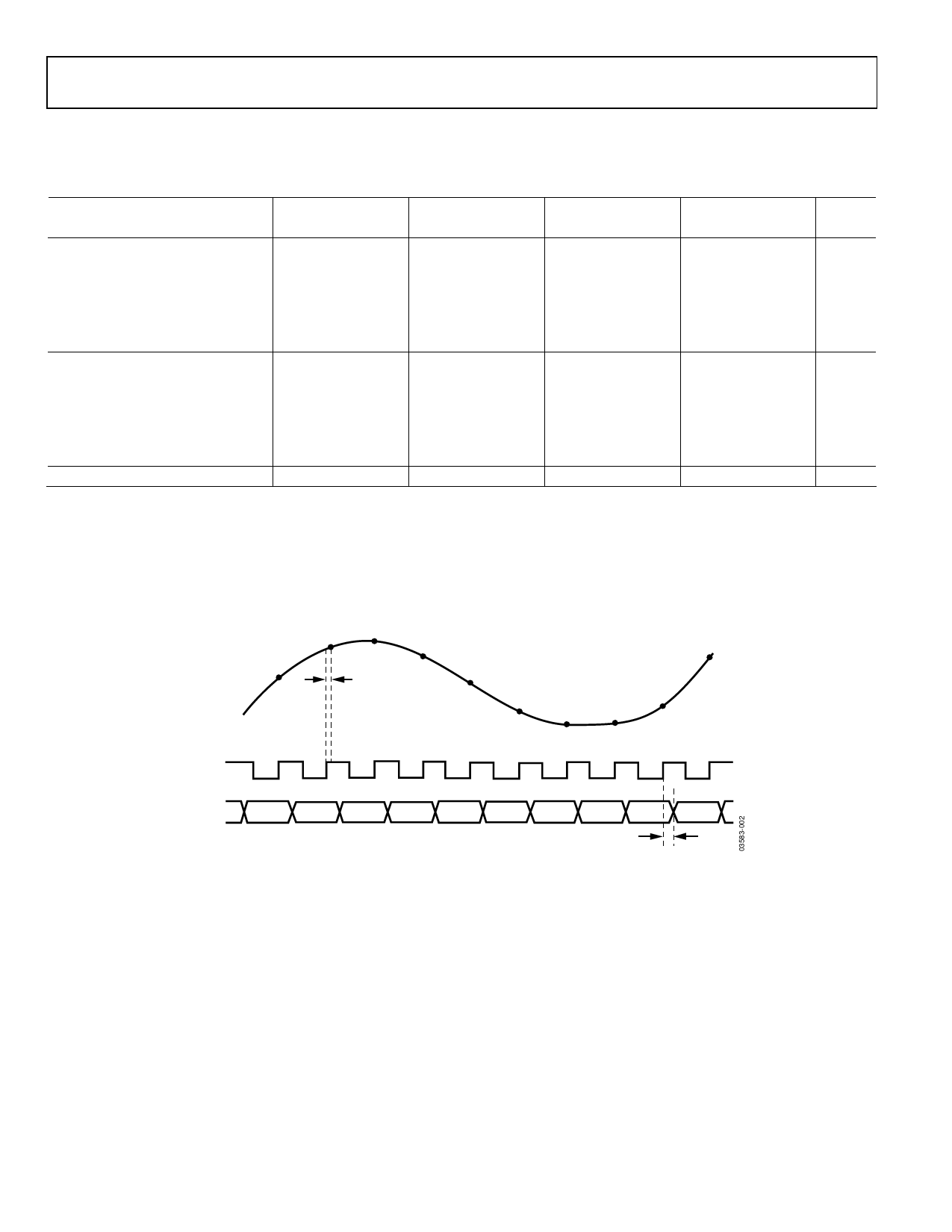

ANALOG

INPUT

N

N+1

N+2

N+8

N–1

tA

N+3

N+4

N+7

N+5 N+6

CLK

DATA

OUT

N–9 N–8 N–7 N–6 N–5 N–4 N–3 N–2 N–1

N

tPD = 6.0ns MAX

2.0ns MIN

Figure 2. Timing Diagram

Rev. D | Page 8 of 32