74HC283 Просмотр технического описания (PDF) - Philips Electronics

Номер в каталоге

Компоненты Описание

Список матч

74HC283 Datasheet PDF : 8 Pages

| |||

Philips Semiconductors

4-bit binary full adder with fast carry

Product specification

74HC/HCT283

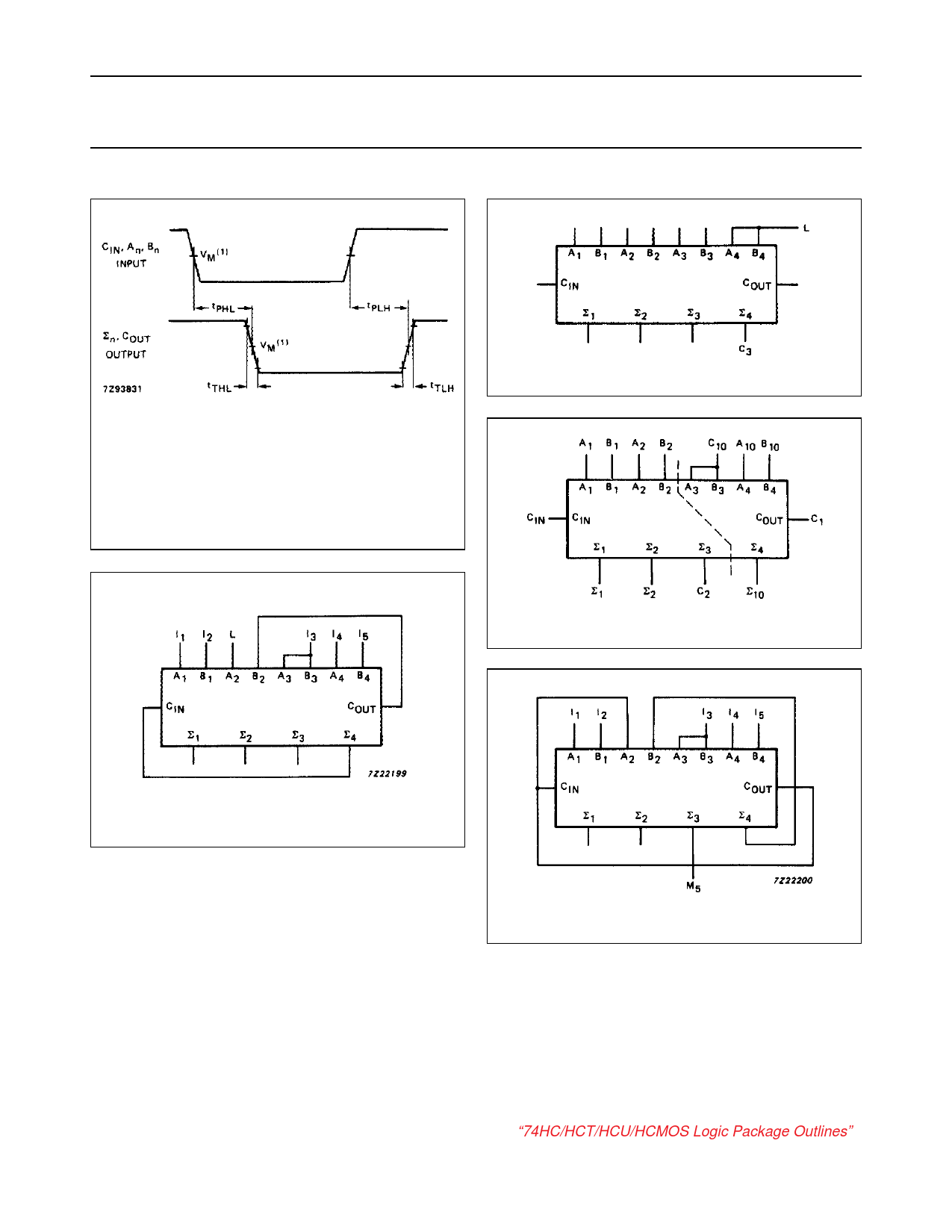

AC WAVEFORMS

APPLICATION INFORMATION

(1) HC : VM = 50%; VI = GND to VCC.

HCT: VM = 1.3 V; VI = GND to 3 V.

Fig.6 Waveforms showing the inputs (CIN, An, Bn)

to the outputs (∑n, COUT) propagation delays

and the output transition times.

Fig.7 3-bit adder.

Fig.8 2-bit and 1-bit adder.

Fig.9 5-input encoder.

Notes to Figs 7 to 10

Figure 7 shows a 3-bit adder using the “283”. Tying the

operand inputs of the fourth adder (A3, B3) LOW makes ∑3

dependent on, and equal to, the carry from the third adder.

Based on the same principle, Figure 8 shows a method of

dividing the “283” into a 2-bit and 1-bit adder. The third

stage adder (A2, B2, ∑ 2) is used simply as means of

transferring the carry into the fourth stage (via A2 and B2)

and transferring the carry from the second stage on ∑ 2.

Note that as long as long as A2 and B2 are the same, HIGH

or LOW, they do not influence ∑ 2. Similarly, when A2 and

B2 are the same, the carry into the third stage does not

influence the carry out of the third stage. Figure 9 shows a

method of implementing a 5-input encoder, where the

Fig.10 5-input majority gate.

inputs are equally weighted. The outputs ∑ 0, ∑1 and ∑ 2

produce a binary number equal to the number inputs (I1 to

I5) that are HIGH. Figure 10 shows a method of

implementing a 5-input majority gate. When three or more

inputs (I1 to I5) are HIGH, the output M5 is HIGH.

PACKAGE OUTLINES

See “74HC/HCT/HCU/HCMOS Logic Package Outlines”.

December 1990

8