74F564PC Просмотр технического описания (PDF) - Fairchild Semiconductor

Номер в каталоге

Компоненты Описание

Список матч

74F564PC Datasheet PDF : 6 Pages

| |||

April 1983

Revised October 2000

74F564

Octal D-Type Flip-Flop with 3-STATE Outputs

General Description

The 74F564 is a high-speed, low power octal flip-flop with a

buffered common Clock (CP) and a buffered common Out-

put Enable (OE). The information presented to the D inputs

is sorted in the flip-flops on the LOW-to-HIGH Clock (CP)

transition.

This device is functionally identical to the 74F574, but has

inverted outputs.

Features

s Inputs and outputs on opposite sides of package allow

easy interface with microprocessors

s Useful as input or output port for microprocessors

s Functionally identical to 74F574

s 3-STATE outputs for bus-oriented applications

Ordering Code:

Order Number Package Number

Package Description

74F564SJ

M20D

20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74F564PC

N20A

20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

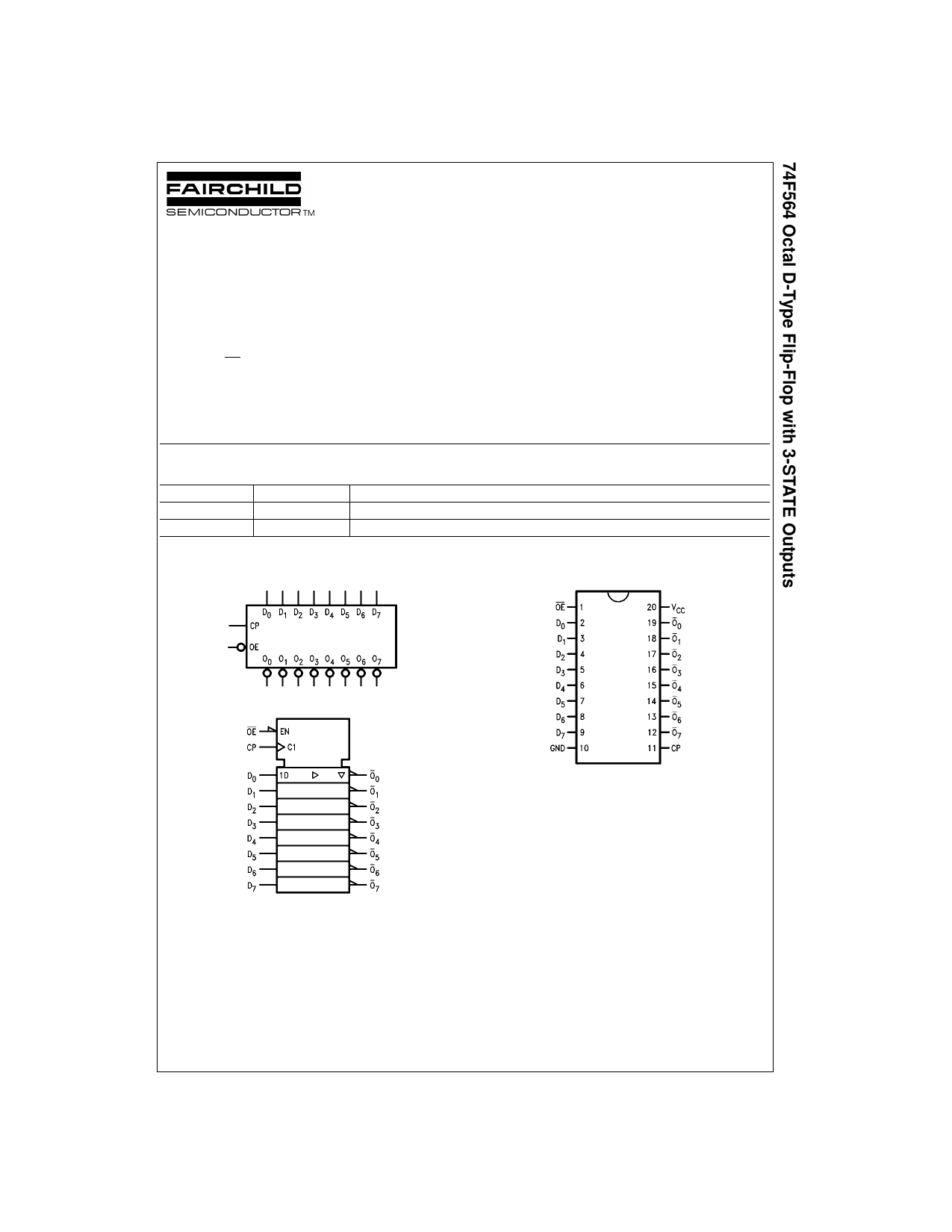

Logic Symbols

Connection Diagram

IEEE/IEC

© 2000 Fairchild Semiconductor Corporation DS009563

www.fairchildsemi.com