MMA7455L(2007) Просмотр технического описания (PDF) - Freescale Semiconductor

Номер в каталоге

Компоненты Описание

Список матч

MMA7455L Datasheet PDF : 27 Pages

| |||

Assigning and Clearing the Interrupt Pins

INT1/INT2 pin assignment for level detection is controlled by Control Register 1 (Address:$18).

$18

CTL1

—

THOPT

ZDA

YDA

XDA INTRG[1] INTRG[0] INTPIN

INTPIN:

0:INT1 will be used for event

1:INT2 will be used for event

Detection status is able to be monitored by Detection Source Register (Address:$0A). Once the configured event is detected,

INT pin or register bit will not be cleared until the respective clear bit (CLRINT1 or CLRINT2) in Interrupt Latch Reset Register

(Address: $17) is set. CLRINT1 and CLRINT2 should be cleared before starting next detection. Otherwise, INT pin or

register will not set.

I

$17

INTRS

—

—

—

—

—

—]

CLRINT2 CLRINT1

NOTE: Measurement period and bandwidth for level detection is different from data output rate and the bandwidth of

“measurement.” Please refer to Functional Parameter for Detection for more information.

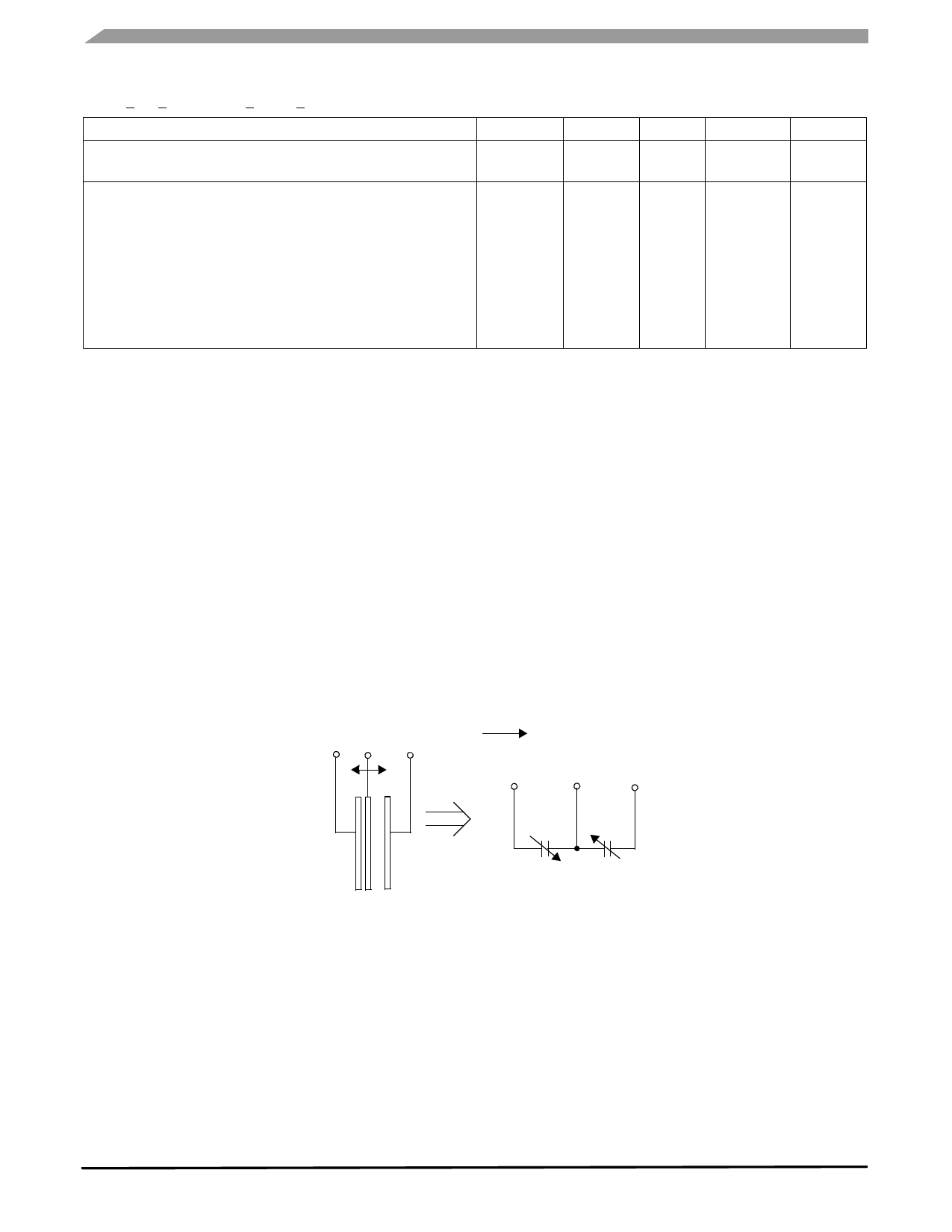

PULSE DETECTION MODE

Pulse Detection Mode

In pulse detection mode, only 8g range is available. It is independent from measurement g-range. Therefore if the measure-

ment range is in the 2g or 4g mode, the pulse detection range will still be 8g. Measurements for x, y and z in 2g/4g or 8g mode

are enabled. The level detection is also enabled in this mode. The pulse detected by the acceleration signal is enabled with single

pulse and double pulse detection allowing the choice of either positive, negative or absolute value pulse detection.

Setting for Motion Detection

For the PDPL bit in Control Register 2 (Address: $19) the register should be set to “0” for motion detection. When the output

value of one of the enabled axes exceeds the threshold limit value, logic high level is output to INT1 or INT2 pin and indicates

the event was detected.

– If PDPL = 0 and all three axes are enabled for detection

– When the condition below was detected, logic high level outputs to INT1 or INT2

– “XOUT ≥Threshold” or “YOUT ≥Threshold” or “ZOUT ≥Threshold”

Setting for Freefall Detection

To configure the MMA7455L for freefall detection, set the PDPL bit in Control Register 2 (Address: $19) to 1 and Time Window

for 2nd pulse value should be “0” for freefall detection. When the output values of all enabled axes are below the threshold limit

continuously during the period specified in Latency Timer Value register, logic high level is output to INT1 or INT2 pin and indi-

cates the event was detected.

– If PDPL = 1, TW[7:0] = 0 and all three axes are enabled for detection

– When the condition below was detected, Logic high level output to INT1 or INT2

– “XOUT ≤Threshold" and “YOUT ≤Threshold" and ”ZOUT≤Threshold"

– INT1/INT2 pin assignment for pulse detection is controlled by Control Register 1 (Address: $18). Detection status is also

able to be monitored by Interrupt Source Register. Once the event was detected, INT pin or register bit will not be cleared

until clear bit in Interrupt Latch Reset Register (Address: $17) is set.

$19

CTL2

—

—

—

—

—

DRVO

PDPL

LDPL

$1E

TW

TW[7]

TW[6]

TW[5]

TW[4]

TW[3]

TW[2]

TW[1]

TW[0]

When the output values of all enabled axes are below the threshold limit continuously during the period specified in Latency

Timer Value Register, logic high level is output to INT1 or INT2 pin indicating freefall was detected.

For a more detailed description of the Threshold Detect please refer to application note AN3571, “Threshold and Pulse Detect

Using the MMA745xL”.

MMA7455L

8

Sensors

Freescale Semiconductor