ZR36057PQC Просмотр технического описания (PDF) - Zoran Corporation

Номер в каталоге

Компоненты Описание

Список матч

ZR36057PQC Datasheet PDF : 48 Pages

| |||

Enhanced PCI Bus Multimedia Controller

11.0 PCI CONFIGURATION SPACE REGISTERS

The PCI specification requires that a PCI device include a con-

figuration register space, a set of 256 8-bit configuration

registers. The first 64 bytes make up the configuration header,

predefined by the specification and the remainder are applica-

tion specific. These registers allow device relocation, device

independent system address map construction and automatic

configurations. The configuration registers are accessed by the

host software through two consecutive doubleword I/O accesses

to physical addresses 0x0CF8 and 0x0CFC, respectively. The

host PCI bridge is responsible for translating these accesses to

a PCI configuration cycle, including the assertion of the IDSEL

input. The ZR36057 then responds to these cycles. This section

details the ZR36057’s PCI configuration registers. PCI configu-

ration accesses to ZR36057 configuration addresses that are

not explicitly described here return zeros (in reads).

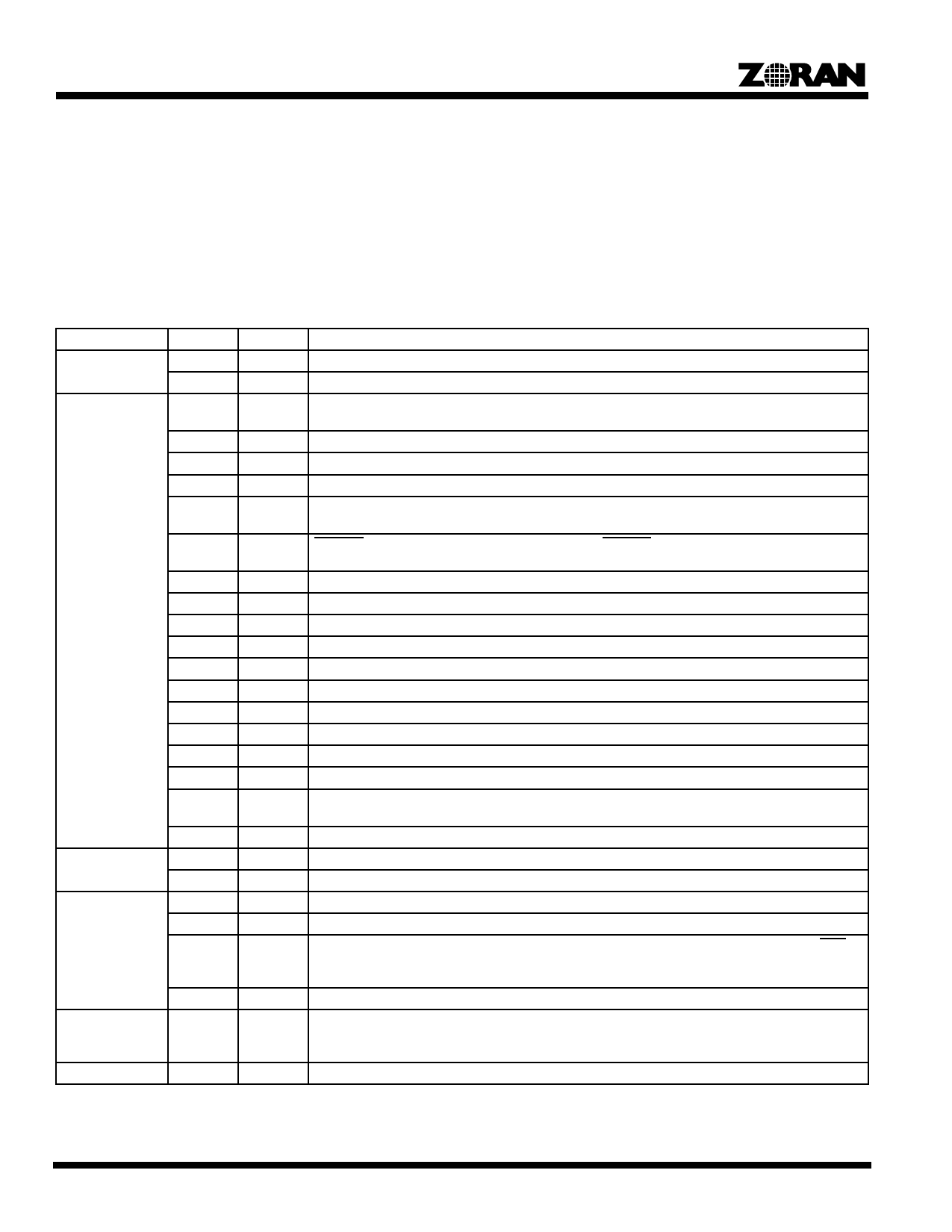

Table 12: ZR36057 PCI Configuration Space Registers

Address Offset

0x00

0x04

0x08

0x0C

Bits

31:16

15:0

31

30

29

28

27

26:25

24

23

22:16

15:10

9

8

7

6

5:3

2

1

0

31:8

7:0

31:24

23:16

15:8

0x10

0x14 to 0x3B

7:0

31:12

11:0

Type

R

R

RC

R

RC

RC

RC

R

R

R

R

R

R

R

R

R

R

RW

RW

R

R

R

R

R

RW

R

RW

R

R

Description

Device ID. Hardwired to 0x6057.

Vendor ID. Hardwired to 0x11DE.

Parity Error Detected. This bit is set when a parity error is detected, regardless of the Parity Error

Response bit.

System Error Signaled. Hardwired to ‘0’.

Master Abort Detected. This bit is set when a master-abort condition has been detected.

Target Abort Detected. This bit is set when a target-abort condition has been detected.

Target Abort Signaled. When the ZR36057 terminates a transaction as a target (e.g., due to wrong

address parity) it sets this bit.

DEVSEL Timing. Hardwired to ‘00’ (“fast” timing, i.e., DEVSEL is asserted before rising edge of clock

three within a cycle).

Data Parity Reported. Hardwired to ‘0’.

Fast Back-to-Back Capability. Hardwired to ‘0’.

Reserved. Returns zeros.

Reserved. Returns zeros.

Fast Back-to-Back Enable. Hardwired to ‘0’.

System Error Enable. Hardwired to ‘0’.

Wait Cycle (Stepping) Enable. Hardwired to ‘0’.

Parity Error Response. Hardwired to ‘0’.

Unused. Hardwired to ‘0’.

Master Enable. When this bit is set to ‘1’ the ZR36057 can operate as a bus master. Default is ‘0’.

Memory Access Enable. When this bit is set to one the device responds to PCI memory accesses.

Default value is ‘0’.

I/O Access Enable. Hardwired to ‘0’.

Class Code. Returns 0x040000 (Multimedia Video Device)

Revision ID. Hardwired to 0x01

Unused. Return zeros.

Header Type. Returns zeros.

Master Latency Timer. The number of PCI clocks that limit ZR36057-initiated bursts in case GNT is

deasserted by the bus arbiter during the ZR36057-initiated burst. The 3 LS bits are read-only zeros.

The default value is 0x00.

Unused. Returns zeros.

Memory Base Address. This value determines the base address of the ZR36057 as a memory-

mapped device. The ZR36057 occupies a range of 4096 bytes out of the memory map: Bits 11:0 are

hardwired to ‘0’. The default value of all other bits is ‘0’.

Hardwired to ‘0’.

24