V61C5181024 Просмотр технического описания (PDF) - Mosel Vitelic, Corp

Номер в каталоге

Компоненты Описание

Список матч

V61C5181024 Datasheet PDF : 12 Pages

| |||

MOSEL VITELIC

V61C5181024

128K X 8 HIGH SPEED

STATIC RAM

PRELIMINARY

Features

s High-speed: 10, 12, 15 ns

s Fully static operation

s All inputs and outputs directly TTL compatible

s Three state outputs

s Low data retention current (VCC = 2V)

s Single 5V ± 10% Power Supply

s Low CMOS Standby current of 5 mA max

s Packages

– 32-pin TSOP

– 32-pin 300 mil SOJ

Description

The V61C5181024 is a 1,048,576-bit static

random-access memory organized as 131,072

words by 8 bits. Inputs and three-state outputs are

TTL compatible and allow for direct interfacing

with common system bus structures. The

V61C5181024 is available in 32-pin SOJ, PDIP and

TSOP.

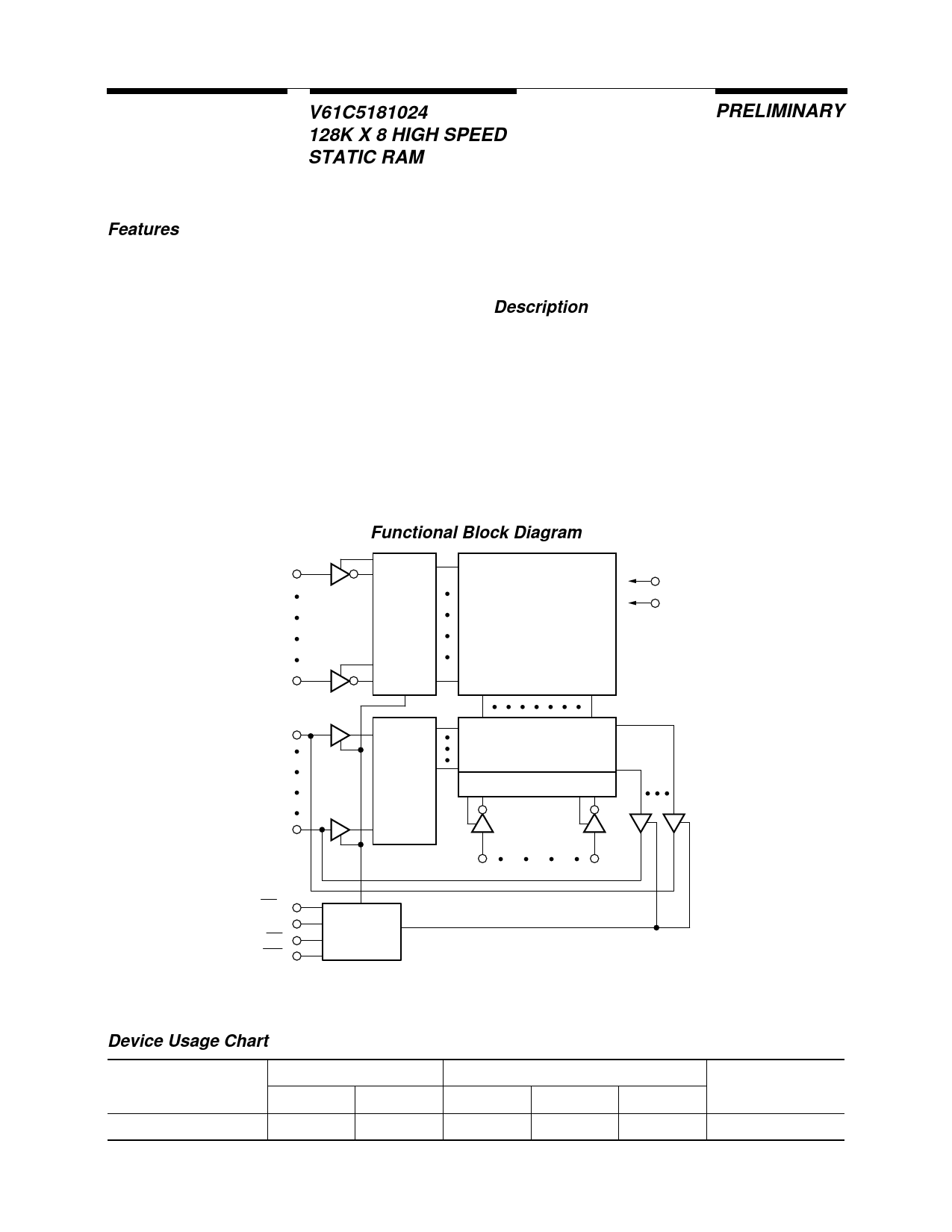

Functional Block Diagram

A0

VCC

Row

Decoder

Memory Array

GND

A8

I/O0

Column I/O

Input

Data

Circuit

Column Decoder

I/O7

A9

CE1

CE2

Control

OE

Circuit

WE

A16

5181024 01

Device Usage Chart

Operating

Temperature

Range

0°C to 70°C

Package Outline

T

R

•

•

V61C5181024 Rev. 1.1 July 1998

Access Time (ns)

10

12

15

•

•

•

1

Temperature

Mark

Blank